-

Posts

52 -

Joined

-

Last visited

Content Type

Profiles

Forums

Events

Blogs

Posts posted by denvys5

-

-

So hot... Wanna see this chip doing 10b ?

-

On 11/6/2021 at 1:13 AM, Leeghoofd said:

What is the name of each core on your Pentium D?

Is core 1 running at the same clocks as core 2?

Can you OC these Pentium D cores individually?

Are both Pentium D cores based on the same technology?

Do both Pentium D cores have the same amount of threads?

Do both Pentium D cores share the same cache?

This set of questions defines what are P+E cores, okay. Change to ADL rankings is designed for future cpus in mind.

My question is: what happens if future E-cores do not check all the requirements? For example, come in same uArch as P cores, do have same amount of threads. We can already see this happening, AMD already talking about this publicly. Looking at modern 2x CCD AMD chips, there is a clear difference between clocks and power for those 2 modules. And they can be clocked separately. In a future, as said in latest public statement, E-core is the same uArch as P-core for them, making further assumptions, maybe less frequency and less cache (like mobile chips right now)

-

-

pizduli have no limits))

-

So that driver works for you, interesting. I had issue with radeon panel not working. You used powerplay tables? Or it just works for you?

-

"Unigine Superposition - 1080P Xtreme - GPU Family"

What rules on subs for SP? *Broken* online Valid? Or the old ways, only screenshot?

-

-

3 hours ago, yosarianilives said:

Vantage (no gddr6/x): Will titans be allowed? Otherwise I like the limitation of no gddr6/x, lowers reliance on EXPENSIVE cards

Vega and Titan V? No gddr6, but yes to HBM

-

1

1

-

-

TeamCup is over, drama keeps flowing.

About flag... I'll tell the story from our team's point of view. We were faced with multiple misconceptions regarding our country selection and name of our team. We had gotten a lot of hate from different CIS communities during TC for our name during competition (USSR_OVER) and our country selection.

Firstly, we created a team with no country specified, but faced a problem: we couldn`t compete in regional ranking (not relevant to TC) at all. So we decided to pick a team based on our team composition - Russia. That generated drama, so we switched to Kazakhstan, and then to Ukraine. That got us more drama, so we switched to another CIS country, which we considered as a neutral choice. We changed national flag to unique one, to limit connections with selected country. Since we mitigated all the initial drama, we were convinced that this choice was truly neutral and did not offend anybody.

For our representation we consider ourselves as an international OC team. We changed name of our team after the end of competition. No drama included, end of story. No politics whatsoever. We didn't want to hurt anyone.

-

4

4

-

4

4

-

-

That was fun, indeed

Local meme went too far ?

QuoteBelarus Team

-

1

1

-

2

2

-

-

-

4 minutes ago, unityofsaints said:

Ideally something fun that really shows the singlecore IPC differences like Pifast or SP1M but SP32M would fit the bill as well imo.

Cinebench single core, maybe? Like R15

Also, y-cruncher was fun to bench. Wanna see more of it ?

For gpu, TSE would be a good addition

^Everything above is only about modern stuff, please, dont force us to run TSE on 775/am2?

-

4.4@1.46V? Thats a very sad cpu :'(

-

On 8/11/2021 at 10:02 PM, denvys5 said:

Question: do we have verification from Intel that P and E cores can do same workload in parallel? Or do they move workload, like on ARM bigLITTLE?

#4 sounds reasonable. I would also add 0P+8E core configuration to that list. Why? Coz we might see 8P+64E cpus in near future, if this architecture succeeds. And that means little cores become competitive in MT benchmarks on their own.

But, this all ranking split is possible only if core configuration can be verified for each individual submission. So 2D only benchmate subs, as far as I understand.

Looking at Intel information on new thread scheduling rules (Intel Thread Director), it makes most sense to do one single ranking for each cpu, by adding up cores. My previous point was based on expectation that cores have different instruction sets. With confirmation that 8E cores are running same instruction set (AVX2 enabled), just as other guys above suggested, 8P+8E = 16C makes the most sense.

-

-

-

Question: do we have verification from Intel that P and E cores can do same workload in parallel? Or do they move workload, like on ARM bigLITTLE?

#4 sounds reasonable. I would also add 0P+8E core configuration to that list. Why? Coz we might see 8P+64E cpus in near future, if this architecture succeeds. And that means little cores become competitive in MT benchmarks on their own.

But, this all ranking split is possible only if core configuration can be verified for each individual submission. So 2D only benchmate subs, as far as I understand.

-

So what ARE the rules on memory stages? Hardware sharing allowed, but RAM sharing no-no? Or no hardware sharing at all, like all other stages?

-

-

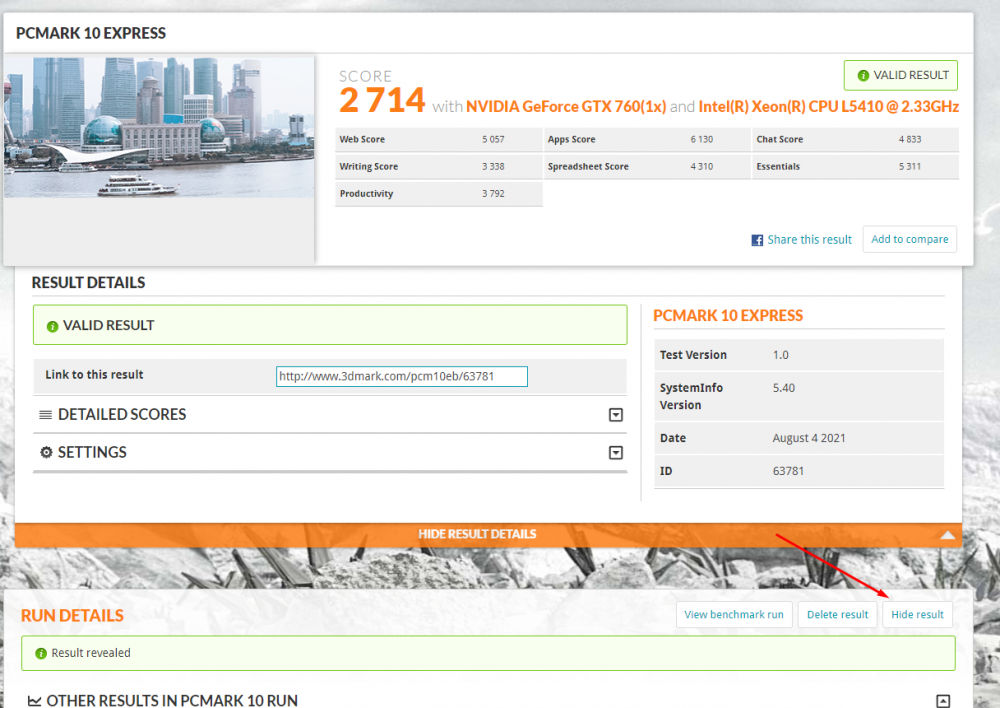

Global score on stock (?) CPU with JEDEC RAM :D

-

Gj beating my 1T score. Looking at clocks, you were really desperate. But smth with your "Effective clock" is not right.

-

13 minutes ago, Leeghoofd said:

Question: HCI keeps on looping or does it stop and give a score in seconds or...

I only know HCI MEMtest Pro which I have for memtesting but never looked for any other functionality

HCI Memtest keeps looping, yes. None of the functionality I have described earlier is present in HCI Memtest itself. It only provides API for this stuff. This allows to design a software solution that would be an actual benchmark (by configuring its setup, performing time-tracking and stopping the process at a defined progress target). I am sorry if I have confused you. There are custom benchmark launchers present on hwbot (e.g. 7zip or y-cruncher), that is why I suggested such idea.

-

41 minutes ago, Leeghoofd said:

How would you rank HCI Memtest ? Doesn't it depend on the mem size, single/dual rank, CPU speed,...

We can define rules, e.g. 6Gb memory for a target of 240% memtest completion with number of threads equal to number of CPU threads. And rank results on the completion time of set target, differentiating them by DIMM type (e.g. DDR4) and, maybe for competitive purposes, number of memory channels that platform supports.

As a result, we would get a competition system, there certain memory configurations pass this memtest faster, by being actually faster in reading, writing and latency-wise (the idea comes from existing one in RyzenDramCalc)

We already have CPU benchmarks, that depend a lot on mem size and/or rank configuration (e.g. GeekBench, y-cruncher). There is some impact from CPU cores/clocks and cache size/clocks, but it is unknown how much does it matter and it can be tested (clearly, memtest is memory bound by default, so going from 9900K 5.0 Ghz to 7.0 Ghz may make little to no difference).

-

Quote

So any ideas of a proper memory benchmark are welcome.

What about integrating HCI Memtest as a memory benchmark?

Like there is one in RyzenDramCalc.

It counts time to perform predefined amount of memtest % with predefined memory-size and with predefined amount of threads

HWBOT 2020 Make it great again Thread:

in HWBOT 2021 Edition

Posted

That may indirectly encourage backups. Coz if implemented system counts only your latest sub, there is no point to improve it ever, unless it is beaten. You may rerun benchmark in the future and get a better score, but you are encouraged to keep that score as a backup by the system.