-

Posts

1708 -

Joined

-

Last visited

-

Days Won

21

Content Type

Profiles

Forums

Events

Blogs

Posts posted by GtiJason

-

-

-

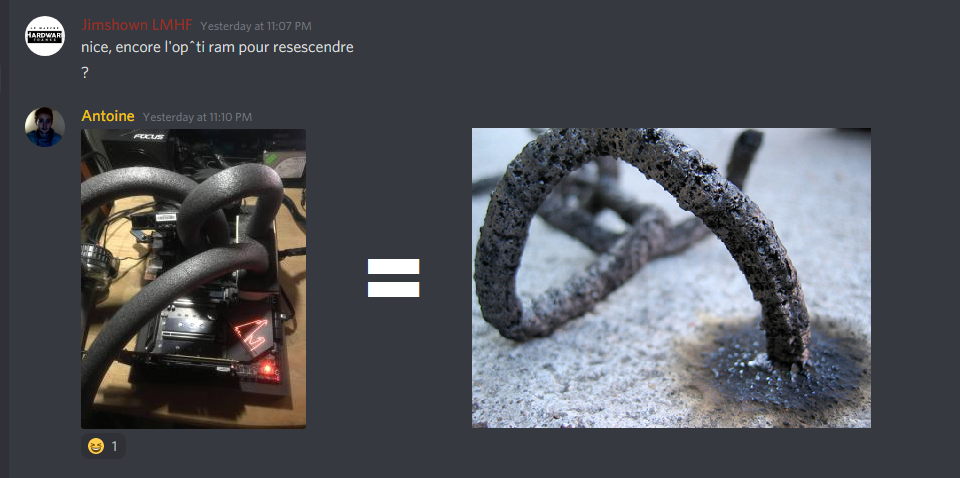

16 hours ago, AxAModder said:

https://cdn.discordapp.com/attachments/577180577091026951/885136927886565436/unknown.png "watercooling custom" :')

You sure that not a school project for elephant toothpaste or maybe Pharaoh's snakes ? ?

-

So Strong, Great benching my friend !

-

-

-

5 hours ago, FUGGER said:

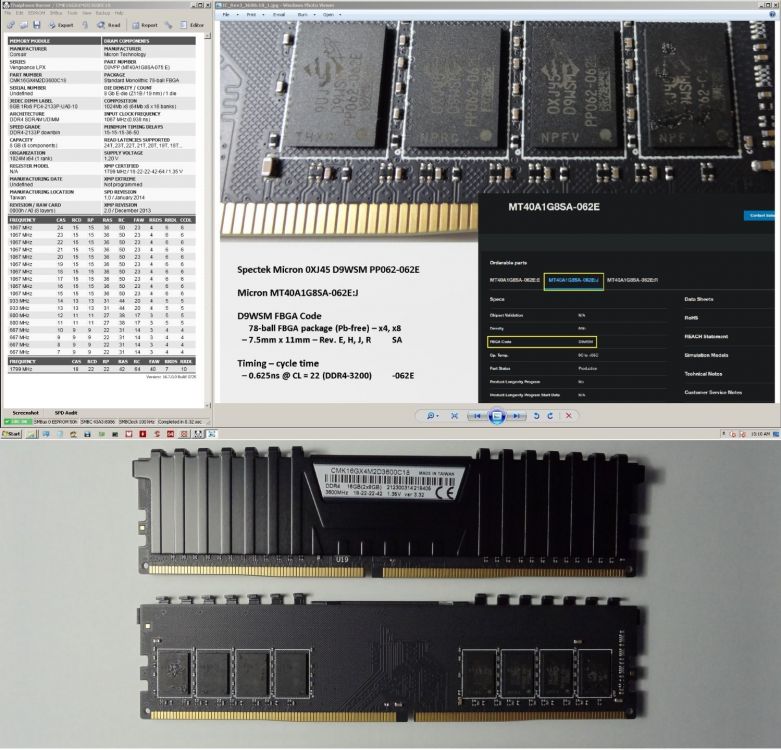

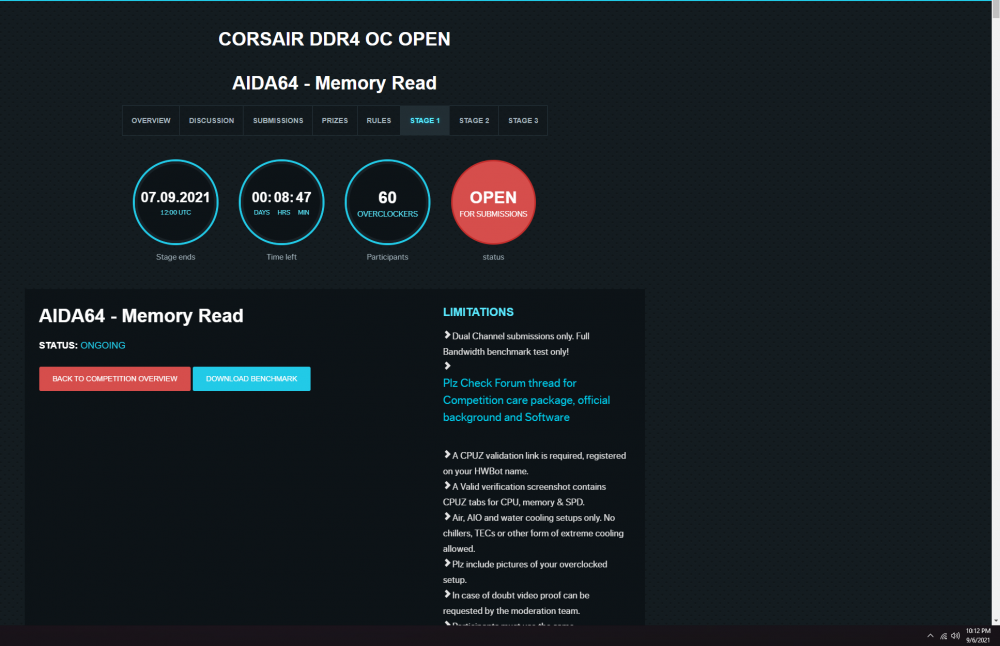

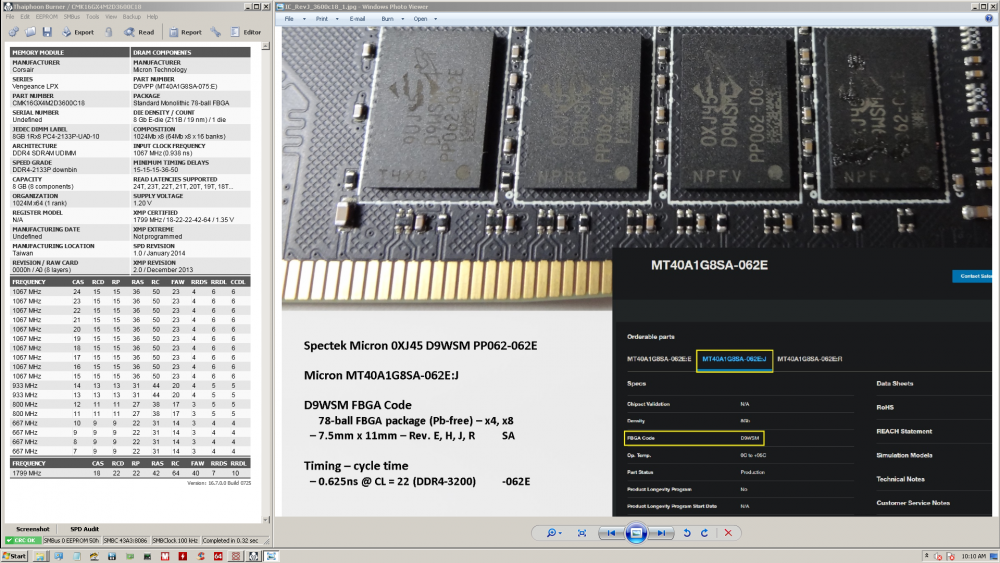

I seem to be the only one with Micron modules ?

I've got Micron's as well (CMK16GX4M2D3600C18 V3.32) , but everyone else is using Samsung besides sabishiihito. He's using a kit similar to mine but actually made for Intel cpu (unlike mine) CMK16GX4M2Z3600C18 Hynix

Have yet to sub mine as cpu (11900Kf) might be on it's way out so probably should use 11600k or 5300G/AMD

-

7 hours ago, GTI-R said:

That's awesome man !

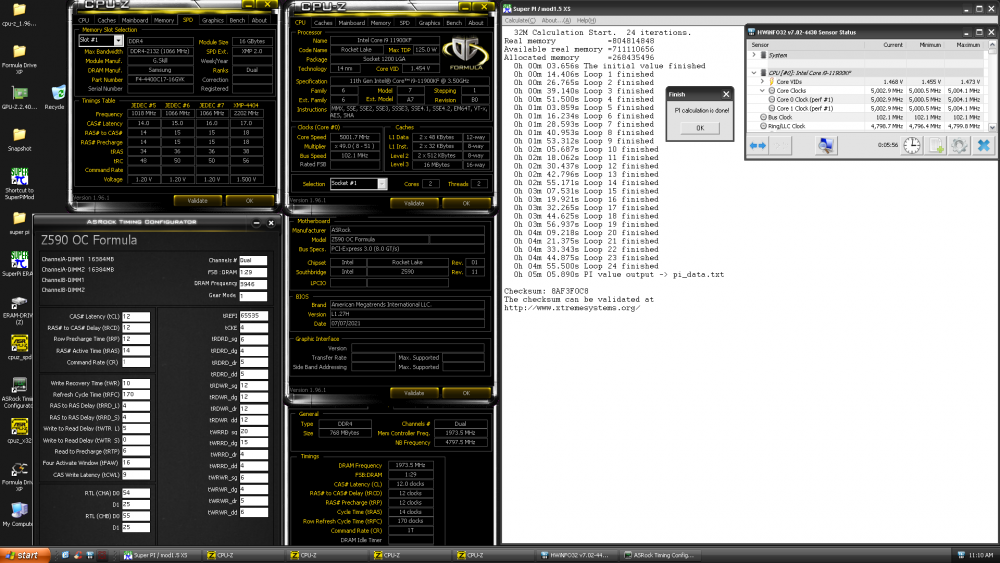

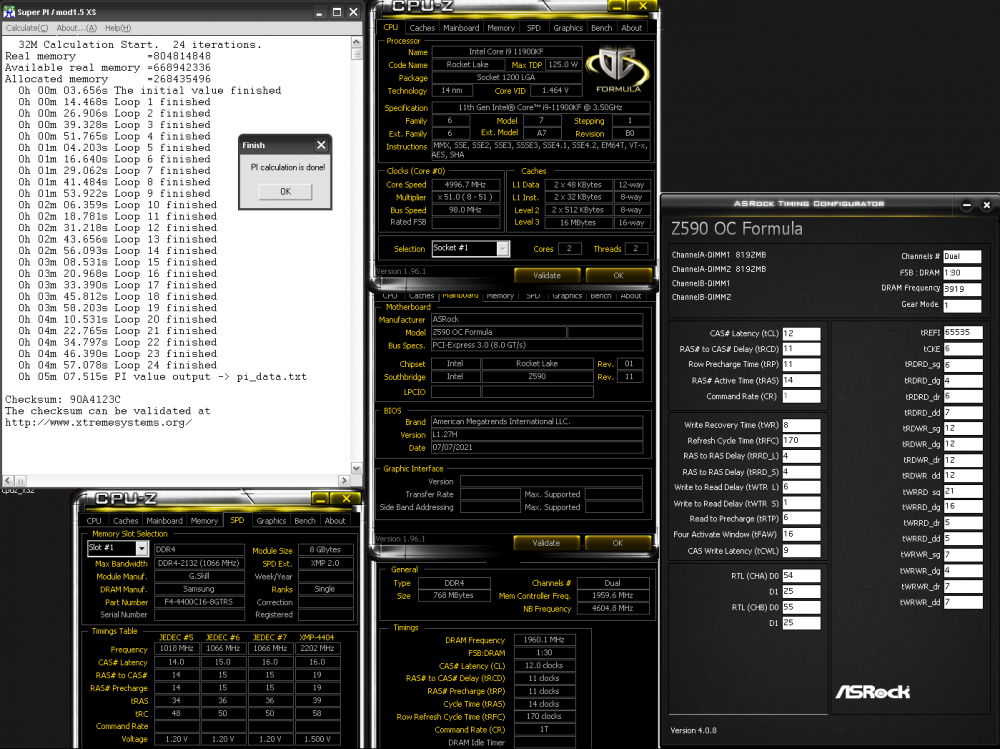

The "best" Dual Rank all ambient Samsung run I have is this. tRCD/RP at 11 seems impossible with this kit.

OS is beyond trashed from testing many kits of memory

Has seen at least 125 NEIR and 25 Not Convergent in Sqr's . ?-

1

1

-

-

13 hours ago, Splave said:

Im not following, 4770k has 4 cores and ht, 9590 has 8 cores. Therefore 4770k is in the 4 core category and 9590 is in the 8 core category proving my argument that 12900k should be in 16

or am i missing something. Its not about what they call, its about what it is. The PR alone I cant wait to hear what they say "worlds fastest big little"/ "first 16 core over 7ghz" etc going to be a real laugh.

or am i missing something. Its not about what they call, its about what it is. The PR alone I cant wait to hear what they say "worlds fastest big little"/ "first 16 core over 7ghz" etc going to be a real laugh.

Exactly, They are in the correct categories. Just saying the argument people used to make about 9590 (and other cpu's like it) that it was made to compete against the 4 core Intel's is not based on logic. I just failed bad at getting my point across ? because I wasn't making an argument for or against anything. I'm not worried about it, I have trust that the correct decision will be made

-

Just to play devils advocate, was the FX 9590 put into 8 core because that's what AMD called it ? What if they had called it a 4 core with SMT, It competed pretty well against the 4770k ? Benchmarks that AMD is usually good at like Cinebench put these 8 cores on par with 4770k when maxxed out on Lin. So were any of these cpu's capable of getting Global First Place back when they were new. I'd imagine CPU Frequency would of been the only one with GpuPi the only other possibility.

I'm not saying to have it one way or not, just want to make sure we are considering everything before making a decision we may regret in the future -

42 minutes ago, GTI-R said:

I'll be referring to this when I use OCF.

I updated the post above so if you took notes they should be changed for better understanding

To clear things up a bit . . .

On some boards, tWR in the UEFI does nothing and instead needs to be controlled through tWRPRE (ASUS). Dropping tWRPRE by 1 will drop tWR by 1, following the rule tWR = tWRPRE - tCWL - 4

On Intel, tWTR_S/_L should be left on auto at first and controlled with tWRRD_dg/_sg respectively. Dropping tWRRD_dg by 1 will drop tWTR_S by 1 and Dropping tWRRD_sg by 1 will drop tWTR_L by 1.

Changing tCWL will affect tWRRD_dg/sg and thus tWTR_S/L. If you lower tCWL by 1 you need to lower

tWRRD_dg/sg by 1 to keep the same tWTR values. This (lowering tCWL) might also affect tWR as mentioned above-

3

3

-

-

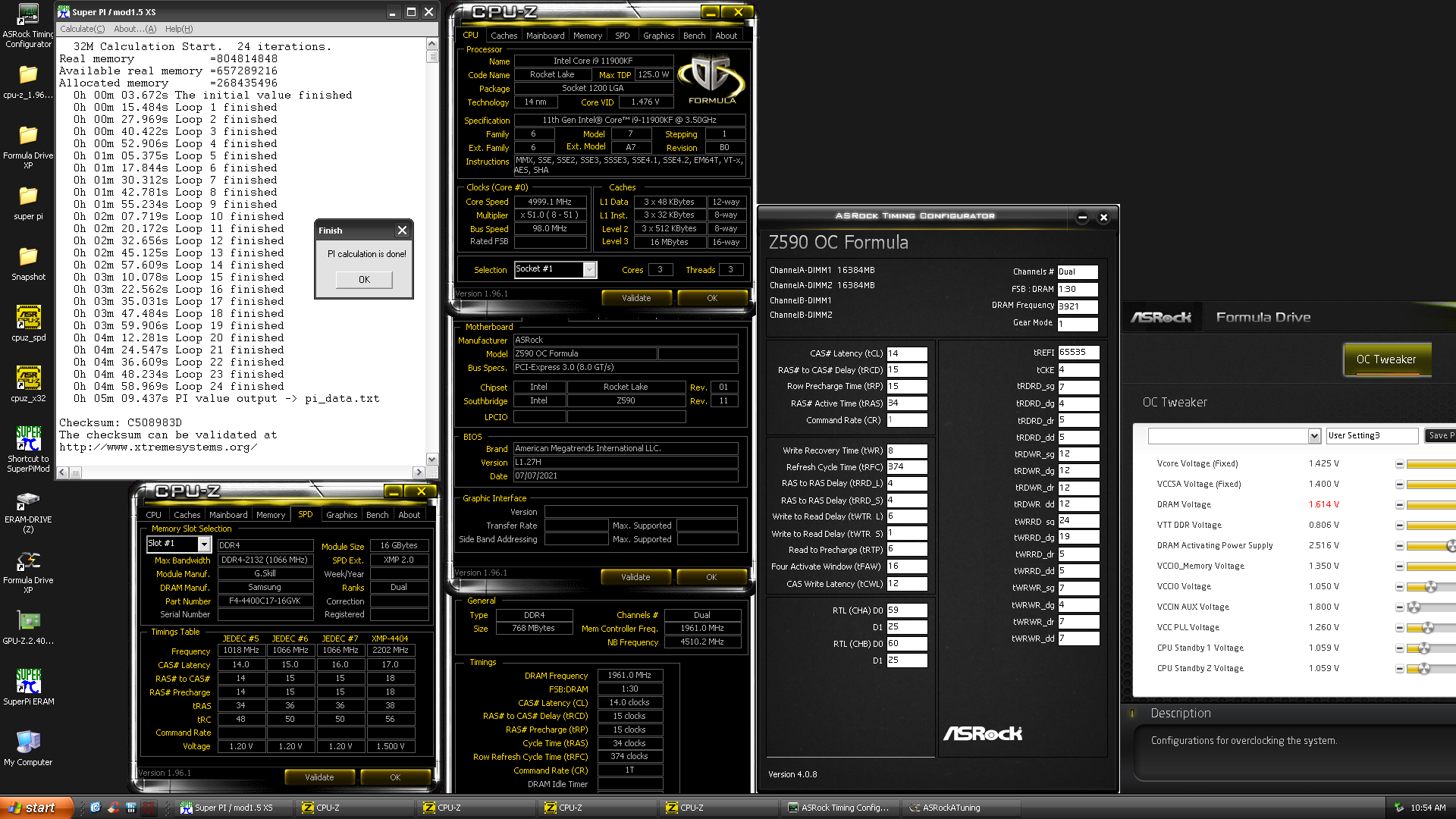

On 8/13/2021 at 5:41 PM, GTI-R said:

I'm currently challenging a 32GB dual rank, but I'm struggling to even boot at 3600mhz!

I can't adjust the third timing.

It's hard.On ASRock OCF or APEX XIII ? If it's OCF make sure to enable XMP in bios

And if the dual rank kit is 2 x 16gb B-Die every kit and cpu I've tried can POST 3866 with 1.410v SA and 1.360v IO Memory or less

For the Special (not so) Secret Sauce try playing with ODT resistances. Try

ODT WR (A1) 120

ODT WR (B1) 120

ODT NOM (A1) 34

ODT NOM (B1) 34

ODT PARK (A1) 48

ODT PARK (B1) 48

You say you have problems with the third timings well look at this image I posted above and copy it.

Try leaving tWRRD_sg and tWRRD_dg on AUTO to start as they are tied to other timings such as

WTR_L, WTR_S, WR, CWL maybe Frequency, CAS Latency (CL) and Command Rate (CR)

Could even try to leave things like WTR_L and WTR_S on AUTO

and maybe even WR because bios does not show tWRPRE or tCCD and

WR = WRPRE - ( CWL + CCD ) . CCD is usually 4 btw

Example WRPRE 28 - ( CWL 9 + CCD 4 )

28 - 13 = 15 so in this case tWR is 15

Last thing is some memory dividers just won't boot or are way harder. So just try a lower or higher divider with BCLK to get desired frequency

EDIT: Just want to clarify things a step further

To clear things up a bit . . .

On some boards, tWR in the UEFI does nothing and instead needs to be controlled through tWRPRE (ASUS). Dropping tWRPRE by 1 will drop tWR by 1, following the rule tWR = tWRPRE - tCWL - 4

On Intel, tWTR_S/_L should be left on auto at first and controlled with tWRRD_dg/_sg respectively. Dropping tWRRD_dg by 1 will drop tWTR_S by 1 and Dropping tWRRD_sg by 1 will drop tWTR_L by 1.

Changing tCWL will affect tWRRD_dg/sg and thus tWTR_S/L. If you lower tCWL by 1 you need to lower

tWRRD_dg/sg by 1 to keep the same tWTR values. This (lowering tCWL) might also affect tWR as mentioned above.

Further Simplified using the Food Chain template haha!

CWL If you lower this by 1

WRRD_sg/dg these lower by 1

WTR_L/S and that makes these lower by 1

WR which raises this 1 by relation of the rule tWR = tWRPRE - tCWL - 4

-

3

3

-

-

9 hours ago, Sparky's__Adventure said:

got any Corsair hahaha

Oh no no no, all mine lol

-

1

1

-

-

Lovin' it !

-

I'll just go ahead and leave this here. BTW the YT comments are amazing !

-

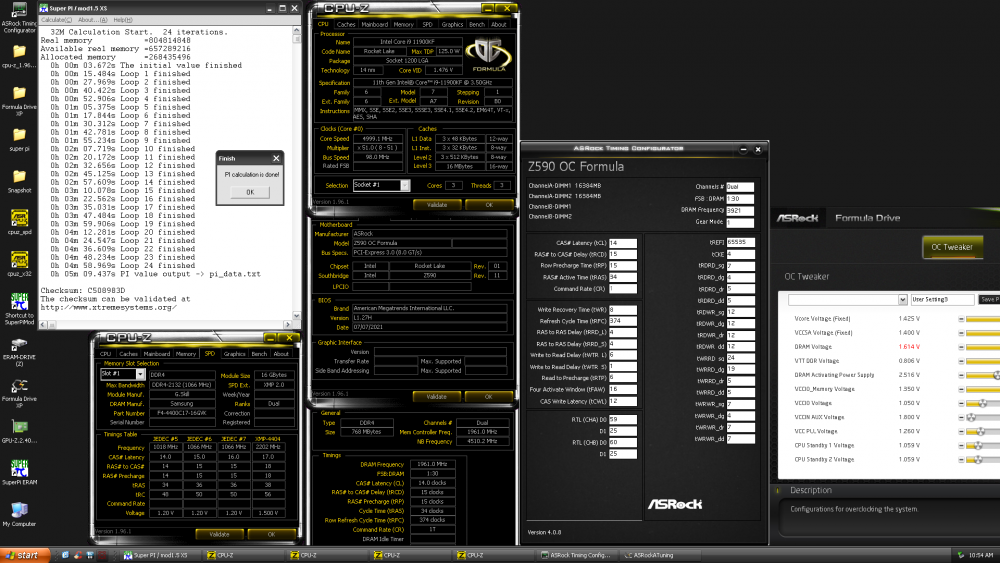

Nice. Geek 3 really only cares about memory bandwidth but real life workloads or Super Pi 32m would love 4066c12 DR at 1:1 for sure. You can even raise several timings reducing latency to maybe gain more bandwidth and GB3 score will probably still go up. I'm betting you can easily do 5000+ c15 at similar voltage as 4800c14 and improve score even more

-

Great job, too bad GB3 doesn't realize the mem score should be more like 13k

-

1

1

-

-

1 hour ago, GTI-R said:

So there's no solution.

I think what Safedisk is trying to say is this . . .

First change PLL Term to 1.05v and CPU Standby to 1.05v while in normal mode

Save and Exit, re-enter the bios then power down

Move LN2 jumper from pins 1-2 to pins 2-3 to change to LN2 mode

Power back on and enter bios to check if LN2 mode is active -

On 8/9/2021 at 8:33 PM, GTI-R said:

VCCIO mem voltage is 1.45V

It's possible that 1.45V is not enough.

Could be. I've had to use 1.600v IOM to get 32m pass 3866+ in Gear 1 using 1T

But I can usually pass 32gb Dual Rank 3866 1T Gear 1 at 1.350v IOM 1.4000v SA.

Also SA sometimes needed to be up to 1.7v

2 x 8gb Single Rank dimms are really hit or miss on Gear 1, they either work or do not work.

Gear 2 5000+c15 etc seems to be where they shine

I don't recommend these settings but I've used them a few times on ambient and so far no problems

Keep in mind, you will fail a Lot !

-

1

1

-

-

-

I know someone mentioned having problems with this board (R3E) so here are the .FZ files I have

Hope they can help-

5

5

-

1

1

-

-

I like it, now get some Industrial PPC or TT Toughfan Turbo's and get that Gold !

-

On 7/15/2021 at 12:26 PM, kimandsally said:

As always a super kind and helpful guy, I have to say the best friend I ever have had in this community, put simply an amazing human being.

Agreed ! Great kindness once again David !

FYI, I'm OUT of the CONTEST-

1

1

-

-

7 hours ago, nnimrod said:

Has anyone other than kingpin binned individual ICs and assembled them? IIRC I saw that set for sale on here awhile ago.

Are you thinking of Allen's custom PSC kit's with 8155KO pcb ?

http://www.xtremesystems.org/forums/showthread.php?286435-I-bin-PSC-per-IC-at-Home-!!

The kit I was lucky enough to get from Splave was not uber good like some of the others but still better than random bin. I gave them to Noxinite when he was having hardware troubles as a little pick me up, plus I wanted to see what he can do with them since I never pushed them very hard-

2

2

-

-

Finally showing off the epic 2 core, must have binned at least 100 according to my data ? ?

ASRock Z590 OC Formula Thread:

in Comet Lake (Z490) & Rocket Lake (Z590) OC

Posted

Yes, lower tCWL to 9 like Ivaneza said

That will allow you to set tWRWR_sg from 23 to 21

and tWRWR_dg from 23 to 21

Lower tWTR_S from 6 to 1

That in turn will allow you to lower tWRWR_dg from 21 to 16