skullbringer

Members-

Posts

57 -

Joined

-

Last visited

-

Days Won

2

Everything posted by skullbringer

-

The official Challenger 2022 Div I Round 1 thread.

skullbringer replied to MaddMutt's topic in HWBOT Competitions

why is a xtu sub getting removed for clock shown in cpu-z? firstly cpu-z clock is not part of the "limitations/rules", secondly cpu-z can't monitor max clock, only current and thirdly that's only recorded at time of the screenshot and not the benchmark, so that makes no sense threefold... -

GIGABYTE Z690 Tachyon

skullbringer replied to sergmann's topic in Alder Lake (Z690) & Raptor Lake (Z790) OC

more voltage on X3I is also needed with Round Trip Latency disabled. Seems more like the X bios are tuned for different terminations (sub zero). Like I also can't boot 6666 on X3I unless I'm exactly at VDD2 1.35, 1.325 doesn't work, 1.375 doesn't work. So also looks like very specific requirements in bios. F6d 6800 doesn't care as long as it's high enough, 1.45 VDD2 no problem. I also think my particular retail Tachyon is not great. Every time I tried your profiles/settings before, it didn't work on my board, so thanks, but let's not do that again -

GIGABYTE Z690 Tachyon

skullbringer replied to sergmann's topic in Alder Lake (Z690) & Raptor Lake (Z790) OC

Any ETA on when RTL tuning will come to official bios? With X3I my CPU and DIMMs do 6666 30-39 2T stable with RTLs 62/57/63/57 -> 13.8k GB3 mem With F6d, I can go higher to 6800 32-41 2T stable and 100 mV less VDD/VDDQ, but without "Round Trip Latency" RTLs end up at 70/68/69/66 -> 13.0k GB3 mem Both is kinda meh imo -

GIGABYTE Z690 Tachyon

skullbringer replied to sergmann's topic in Alder Lake (Z690) & Raptor Lake (Z790) OC

So what's the best bios for memory OC with 12900K (not S) and which GTL version goes with it? Should I just grab the latest version (lowest down link in OP) each? -

The official Challenger 2022 Div I Round 1 thread.

skullbringer replied to MaddMutt's topic in HWBOT Competitions

So then this stage implies "all P cores enabled" because there is no 12900K(2P)? or is it allowed to set the CPU to G7400 so the calculation is actually done based on 2 P cores enabled? -

The official Challenger 2022 Div I Round 1 thread.

skullbringer replied to MaddMutt's topic in HWBOT Competitions

also why is the score always getting devided by 8, no matter how many cores are enabled? shouldn't it be 16 then for the 12900K?! -

The official Challenger 2022 Div I Round 1 thread.

skullbringer replied to MaddMutt's topic in HWBOT Competitions

any ideas what's causing the xtu monitoring to be off by several hundred MHz im my case? -

Gigabyte Z590 XOC Bios/Tools

skullbringer replied to SparkysAdventure's topic in Comet Lake (Z490) & Rocket Lake (Z590) OC

Honestly I can't say for sure anymore as this was quite some time ago. It's possible that I made an error there, that the board was capable pf running 3866 devider with one of the bios versions current at the time and I might have done my final round of testing on the other bios (must have been F5 iirc). So if you're looking for an error in my testing, I can't prove the contrary. Though I don't think it would chang much regarding the overall conclusion. And having to hop between bios versions for gear 1 or gear 2 optimizations also wouldn't help much either frankly. -

Gigabyte Z590 XOC Bios/Tools

skullbringer replied to SparkysAdventure's topic in Comet Lake (Z490) & Rocket Lake (Z590) OC

3 months between those screenshots and the review and a lot of bios versions. review was done with latest available at the time, which could not do 3866 divider -

GIGABYTE Z690 Tachyon

skullbringer replied to sergmann's topic in Alder Lake (Z690) & Raptor Lake (Z790) OC

you also can't set it down via gtl, though you can set it up. sure, you don't need bclk minus often, but when you needed it's usually in a situation where it's really annoying if it doesn't work -

GIGABYTE Z690 Tachyon

skullbringer replied to sergmann's topic in Alder Lake (Z690) & Raptor Lake (Z790) OC

I think radio buttons are also buggy with this bios version, you can go up bclk with +, but not down with - in Germany we call this an Einbahnstraße -

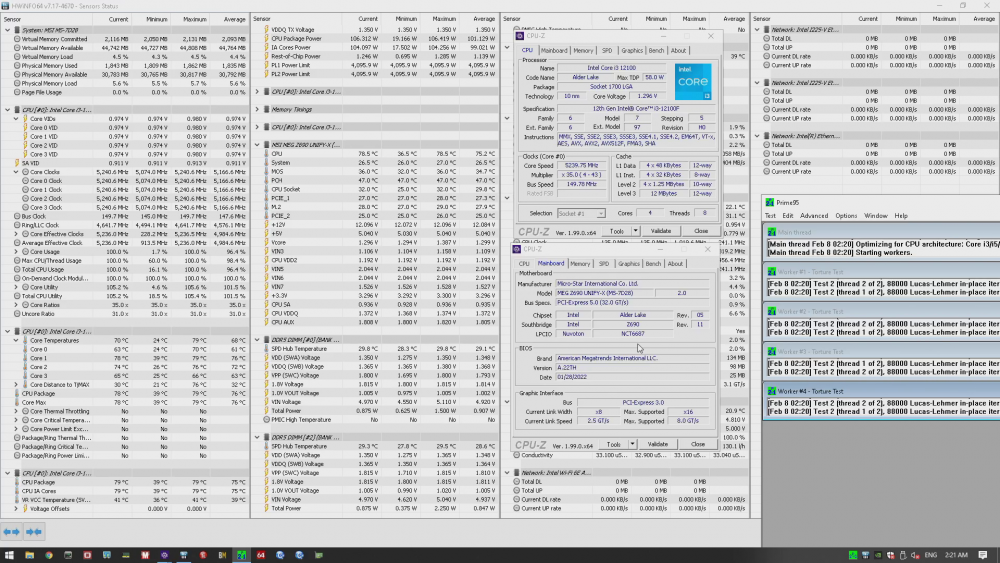

here's bios a22 releases for unify-x for specific cpu steppings. first bios versions that support non-k cpu oc at least from my testing C is for C0 stepping CPUs, H for H0 stepping https://drive.google.com/drive/folders/1bpIeE97M_FfBGT3xrS2IIl8Z4yR4aFST?fbclid=IwAR2JbsiaDbaPJIjaasYfuaZPCoqQTsDlXeo7pIgLndLMbrQdK6gdnyKEgHA proof, running i3-12100F in p95 small fft at 5.2+ GHz:

-

GIGABYTE Z690 Tachyon

skullbringer replied to sergmann's topic in Alder Lake (Z690) & Raptor Lake (Z790) OC

it boots 6800 in 1 of 30 tries, so i'd rather keep this memory training state then instead of having to do another 30 post loops each time I crash ? -

GIGABYTE Z690 Tachyon

skullbringer replied to sergmann's topic in Alder Lake (Z690) & Raptor Lake (Z790) OC

did some benching last night as well on x2i, it once trained 6800 with tight rtl's and was gb3 stable, then never trained 6800 again. also had to do a few power offs and clear cmos to recover from 28 - 54 loops... is sa locked on non-k chips btw? on the filp side, once it had trained at reasonable speed and timings, doing the bclk oc was really easy and straight-forward. also gtl for cache and p core multi worked great! https://hwbot.org/submission/4911303_ -

GIGABYTE Z690 Tachyon

skullbringer replied to sergmann's topic in Alder Lake (Z690) & Raptor Lake (Z790) OC

thanks for sharing the new bios! it can't do 1T yet, can it? i've tried it a few times and always get straight 28->54 -

GIGABYTE Z690 Tachyon

skullbringer replied to sergmann's topic in Alder Lake (Z690) & Raptor Lake (Z790) OC

Cheers, thanks for the update! -

GIGABYTE Z690 Tachyon

skullbringer replied to sergmann's topic in Alder Lake (Z690) & Raptor Lake (Z790) OC

anyone know eta on command rate, rtl and avx512 settings? last bios updates are almost 1 month old -

Gigabyte Z590 XOC Bios/Tools

skullbringer replied to SparkysAdventure's topic in Comet Lake (Z490) & Rocket Lake (Z590) OC

Here's some screenies for you. 3866x102, 1.65 SA, 1.6 IO 2/Mem, 1.9 Vdimm, 0.9 VTTDDR. Forcing a memory retrain by going to limp mode and then F10 without any changes, gives me either of the two sets of RTLs, but never anything in between. -

Gigabyte Z590 XOC Bios/Tools

skullbringer replied to SparkysAdventure's topic in Comet Lake (Z490) & Rocket Lake (Z590) OC

Holy shit, GTL is easy to use and works so well, thx for linking! On another note, has anyone manged to reliably and consistently train RTLs on the Tachyon? On 2Xg it keeps flapping for me between 68-67 and 55-56 from training to training, which looks like opportunistic Round Trip Latency disable or enable, like you can manually set on Asus, but I haven't found such setting in the Tachyon bios yet. When I manually set them to either of the auto combinations above, it only trains successfully in about 1/10 attempts, otherwise fails (55) and enters recovery mode -

ROG Maximus XII Apex

skullbringer replied to FireKillerGR's topic in Comet Lake (Z490) & Rocket Lake (Z590) OC

yeah rkl, sorry should have mentioned. think the m13a does a lot better, but the m12a doesn't seem to have that optimization yet for dr b-die. -

ROG Maximus XII Apex

skullbringer replied to FireKillerGR's topic in Comet Lake (Z490) & Rocket Lake (Z590) OC

Has anyone managed to get DR B-Die Running above DDR4-4400 on the M12A? Seems like I am hitting a hard wall there, no matter which bios version or settings -

skullbringer - DDR4 SDRAM @ 2550MHz - 2550 MHz Memory Frequency

skullbringer replied to keeph8n's topic in Result Discussions

just pasting it here, since I can't find where I'm supposed to enter it: https://browser.geekbench.com/geekbench3/8905813

.thumb.png.631b52017057364d125272ebe5d18f76.png)

.thumb.png.8d4c5178e03ffa03e07c5754f411d51b.png)