-

Posts

534 -

Joined

-

Last visited

-

Days Won

17

Content Type

Profiles

Forums

Events

Blogs

Everything posted by safedisk

-

Hi Bro Which cpu do you use? G.SKILL NEO IC b-die? Can you tell me your setting voltage? Thank you

-

safedisk - Core i9 10900K @ 7461MHz - 4min 1sec 766ms SuperPi - 32M

safedisk replied to Don_Dan's topic in Result Discussions

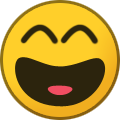

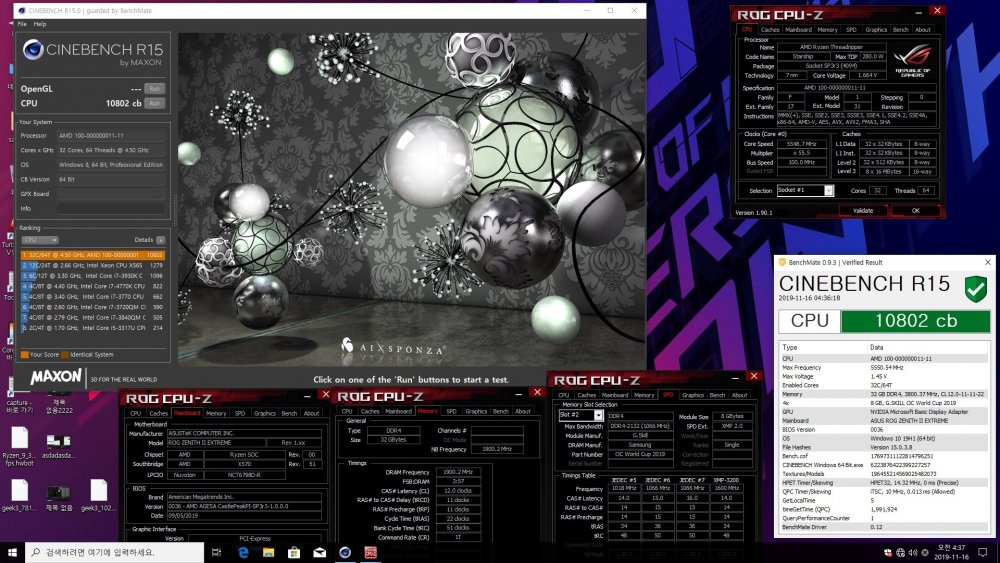

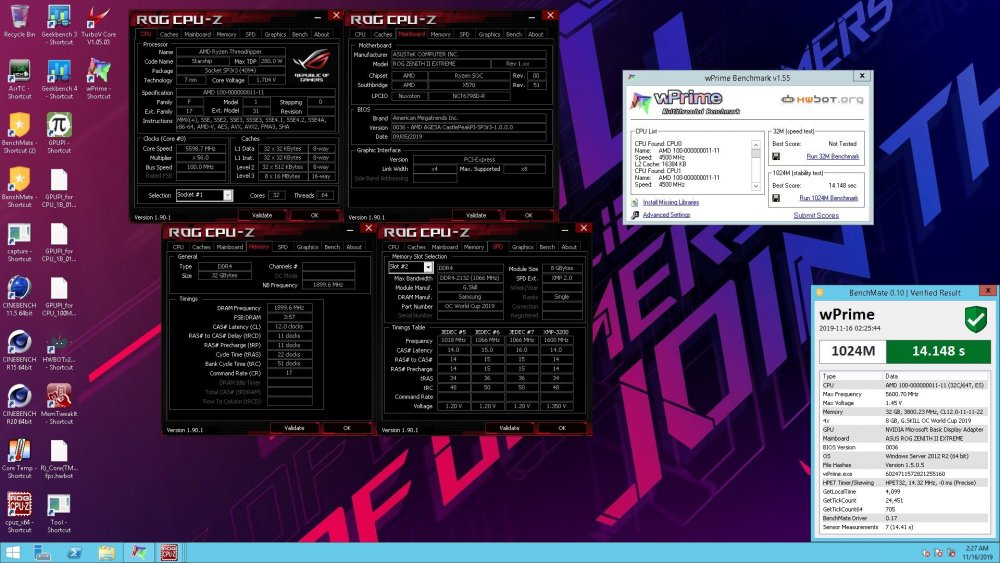

Thank you! all guys This is the result of LN2. ? -

ROG Maximus XII Apex

safedisk replied to FireKillerGR's topic in Comet Lake (Z490) & Rocket Lake (Z590) OC

nice! -

Alex@ro - DDR4 SDRAM @ 3277.3MHz - 3277.3 MHz Memory Frequency

safedisk replied to Leeghoofd's topic in Result Discussions

nice job! -

OGS - Core i7 2600K @ 5970MHz - 5min 33sec 750ms SuperPi - 32M

safedisk replied to Leeghoofd's topic in Result Discussions

Nice job! -

ROG MAXIMUS XII APEX first shots:

safedisk replied to Leeghoofd's topic in Comet Lake (Z490) & Rocket Lake (Z590) OC

you are lucky I do not have a retail motherboard. haha -

ROG Maximus XII Apex

safedisk replied to FireKillerGR's topic in Comet Lake (Z490) & Rocket Lake (Z590) OC

Ready! -

ROG Zenith II Extreme LN2 OC Guide

safedisk replied to safedisk's topic in Ryzen | Bristol Ridge AM4

Depends on cpu- 15 replies

-

- 1

-

-

ROG Zenith II Extreme LN2 OC Guide

safedisk replied to safedisk's topic in Ryzen | Bristol Ridge AM4

Thanks! mate- 15 replies

-

LN2 BIOS ROG ZENITH II EXTREME 0036 BIOS DOWNLOAD : https://bit.ly/36aJALz Official BIOS ROG ZENITH II EXTREME 0602 BIOS DOWNLOAD : https://bit.ly/2rngx8Y 01.Update AURA Led FW version to 0202. 02.Update AGESA BIOS code to the latest PI1.0.0.2 03.Improve system performance. Before running the USB BIOS Flashback tool, please rename the BIOS file (Z2E.CAP) using BIOSRenamer. OCPACK Turbov and CCX OC Tools : https://bit.ly/2REIMef MemTweakIt : https://bit.ly/2UhX8An Zen Perfboost : https://bit.ly/34W7hap (After loading CineBench R15 or Geekbench3 bench then run the boost, just click defaults button after benching to prevent bsod) USB Flashback LN2 OC TIP Enable LN2 mode, Use the Load LN2 profile as a base template, this uses low vcore so you can save exit when it’s not cold around 0C. You will need to do this before -40C to avoid cold bug. (note, ln2 profile disables some usb ports) Always press reset if hang 94 for bios 1,, 07/20/21 post codes also can press reset many times to try Typically when running 8 sticks, the FCLK margin is slightly worse. To improve margins on the Fabric, two key rails to control are VDDG IOD and VDDG CCD voltage and SOC voltage. VDDG is sourced from SOC voltage and therefore will not be able to exceed SOC voltage. On ambient 1.0 VDDG CCD + 1.10 VDDG IOD is enough to max out FCLK. On LN2 you want around 0.9 VDDG IOD and 1.20 VDDG CCD. On the chipset, when bclk is overclocked, the SATA would all drop out. For BCLK oc use a pcie raid card or NVME, and this will do. Typically margins would be better for devices under the CPU PCIE lanes. TRY NOT TO CLEAR CMOS WHEN CPU IS COLD IF you clear cmos, FCLK will go back to Auto and CLDO VDDG voltage will too. When cold, FCLK needs to be 1400+ and VDDG voltages if not Fabric will be unstable so you need to torch up to maybe -60c in this case. There is an FCLK cold bug under LN2 so try to stay around 1400~1600 for FCLK under LN2 to get a good compromise between temps and perf. To improve stability in this case: 0.9 VDDG IOD and 1.20 VDDG CCD, SOC 1.35v, disable DF Cstates. ~ 40% cpus have no CB when fclk is 1400 with these settings. Depending on the CPU and FCLK, may have to control temps -120C ~ -170C. Typically on ln2, with 1.55vcore and -160++C 5.3~5.5 should run cinebench. Use performance bias to improves scores, CBAggressive will BSOD within 1 minute so use the tool to execute it then bench then execute Gentle or defaults after bench. Post codes Hang 92/98 too high VDDG CCD Hang 90/07 too high fabric/ fabric unstable Hang 20/21 too tight timings, can reset a few times to try to pass. Hang 94, often with LN2 bios, can press reset. Enjoy!

- 15 replies

-

- 2

-