Antinomy

-

Posts

1987 -

Joined

-

Last visited

-

Days Won

53

Content Type

Profiles

Forums

Events

Blogs

Posts posted by Antinomy

-

-

On 7/14/2021 at 5:53 AM, Leeghoofd said:

S478 is the socket of preference

s478B only, I presume?

Intel DDR2 - is FB-DIMM counted as DDR2?

-

On 7/26/2021 at 7:03 AM, yosarianilives said:

Saw the new restriction of 2p max, it solves everything.

Well, yes but I hope the restrictions are not gonna change during the competition. I was hoping for a nice challenge with MrPaco.

-

On 7/23/2021 at 11:26 PM, digitalbath said:

some BIOSes use 6:6 ratio register, and some use 4:4 (DFI). Is there a difference? Both are 1:1 FSB:DIMM ratio.

Maybe it's just different straps with same 1:1 divider? If it's true, 6:6 is 1/1 on FSB200, 4:4 is 1/1 on FSB 133.

On 7/23/2021 at 11:26 PM, digitalbath said:Sometimes cpu-z detects twice the number of dimms. When using only one dimm in ASRock K7NF2, CPU-Z detect most CL2,0, not CL2,5 or CL3,0.

see here: https://valid.x86.fr/xexj6t

I guess that are minor Problems. Cheating FSB:DIMM ratio is more crucial.

Just make a report and write to Franck, he does respond quickly most of the time.

-

Excellent score!

-

Nice score! Hope it's not the final.

-

1

1

-

-

Тяжёлая артилеррия пошла, поздравляю!

-

On 7/6/2021 at 4:06 AM, I.nfraR.ed said:

Reticle site is always 1 - it's either a mistake in the tweaker

Nope, I've cross-checked all my CPUs with tweaker and CPUMSR, they both show always 1.

On 7/6/2021 at 4:06 AM, I.nfraR.ed said:the only core that has 1 instead of 0 is Thoroughbred B (as in "the 2nd revision of T-Bred core")

Now that is interesting. So the major revision is the same thing as core revision (stepping in terms of CPUID) and minor revision is the suffix for it. So it's like Thoroughbred-B.14 or rev. B0.14...

Another interesting thing is that minor revision is not an absolute build number.

So we can see 0.14 and 1.2 meaning that minor revision works only together with major. It's only important for Thoroughbreds and maybe Palomino because Bartons are all same major revision. -

5 hours ago, Leeghoofd said:

Yes you need a registered version to validate on their site

Thank you. I don't have problems to buy certain benchmarks, I just can't catch up with all them changing around. Half a year ago I bench them all one way, now half of them doesn't work that way anymore.

Another reason why 3D01, Spi, Pifast are my favourite

-

On 1/30/2021 at 2:41 AM, Leeghoofd said:

UNIGINE SUPERPOSITION SERIES

Unigine is another pay2win app?

Or is there a way to validate the free edition? Couldn't find it, any guides for oldies? -

Congratulations on defeating the great Terraraptor and Gradus!

-

1

1

-

-

37 minutes ago, Tzk said:

Wouldn't it be better if we could open that info box with a button inside the tweaker?

This is just a test build. We don't even know, if we need this info in the future. For timings you can use the regular version.

-

1

1

-

-

10 hours ago, Tzk said:

@Antinomy A question regarding the forums and its editor: Is there a possibility to install a plugin for the WYSIWYG editor to include tables? The table above was just copy&paste from excel, but i can't change the table width... Not sure how you did it in your post.

Reticle site was 1 for all my CPUs. I've made copy and paste from Google docs, width pasted a bit more narrow than in my table, had to make it a bit more wide.

-

1

1

-

-

CPU model Stepping Week Stepping Locked/unlocked Processor code Major Minor Type EdValue Crystal marker Athlon XP 2500+ AQXEA 0330 WPMW Unlocked Barton 0 12 Unlocked 2316h Unknown Athlon XP 2500+ AQZFA 0411 SPMW Locked Barton 0 2 Locked 2306h AQYFA Athlon XP 2500+ AQXEA 0327 SPGW Unlocked Barton 0 12 Unlocked 2316h Unknown Athlon XP 2500+ AQZFA 0350 SPMW Locked Thorton w/512K 0 11 Locked 2315h AQYFA Athlon XP 2500+ AQZFA 0347 VPMW Locked Barton 0 2 Locked 2306h AQYFA Athlon XP 2600+ AQYFA 0410 VPMW Locked Thorton w/512K 0 11 Locked 2315h AQYFA Athlon XP 2600+ AQYFA 0410 VPMW Locked Thorton w/512K 0 11 Locked 2315h AQYFA Athlon XP 2600+ AQXEA 0407 UPMW Locked Barton 0 12 Unlocked 2316h Unknown Athlon XP 2600+ AQZFA 0405 VPBW Locked Barton 0 2 Locked 2306h AQYFA Athlon MP 2800+ AQYHA 0416 UPAW Unlocked Thorton w/512K 0 11 Locked 2315h AQYFA Athlon MP 2800+ AQYHA 0416 UPAW Unlocked Thorton w/512K 0 11 Locked 2315h AQYFA Athlon XP 3000+ AQYHA 0437 CPJW Locked Thorton w/512K 0 11 Locked 2315h AQYFA Athlon XP 2600+ SFF AQYHA 0351 MPMW Locked Thorton w/512K 0 11 Locked 2315h AQYFA Athlon XP-M 2500+ AQXFA 0337 XPMW Unlocked Barton 0 2 Locked 2306h AQYFA Athlon XP-M 2500+ AQYFA 0342 MPM Unlocked Thorton w/512K 0 11 Locked 2315h AQYFA Sempron 3000+ ADYHA 0512 MPMW Locked Thorton w/512K 0 11 Locked 2315h AQYFA Sempron 3000+ IQYHA 0444 VPMW Locked Thorton w/512K 0 11 Locked 2315h AQYFA -

1

1

-

-

Quote

Very easy score, should be more in it."

Ne spali k heram

-

1

1

-

1

1

-

-

1 hour ago, I.nfraR.ed said:

NF3 and NF4 bioses also use "E4", although I don't know how relevant it is.

Might be more than relevant - "NVMM" http://www.rcollins.org/

QuoteSolely designed and implemented NVIDIA memory module reference code (NVMM).

n Revolutionary new design to work with any BIOS vendor, any CPU, North Bridge, South Bridge, and Super IO.

n This design reduced code size, increased maintainability, and substantially reduced the support role of NVIDIA AEs for NVIDIA chipsets.

1 hour ago, I.nfraR.ed said:Maybe it's worth checking performance of the bioses "as-is" on a real Ultra B first, with same manual settings on diffrerent benchmarks, but that's a lot of work.

Yes, I agree on this. Have two DFIs...

-

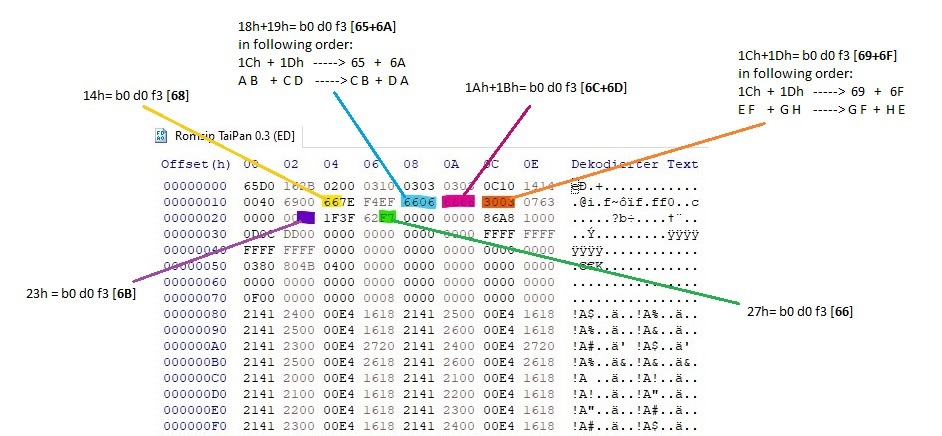

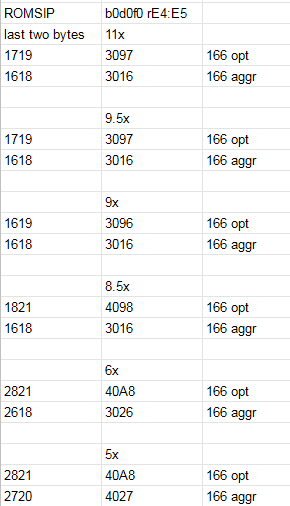

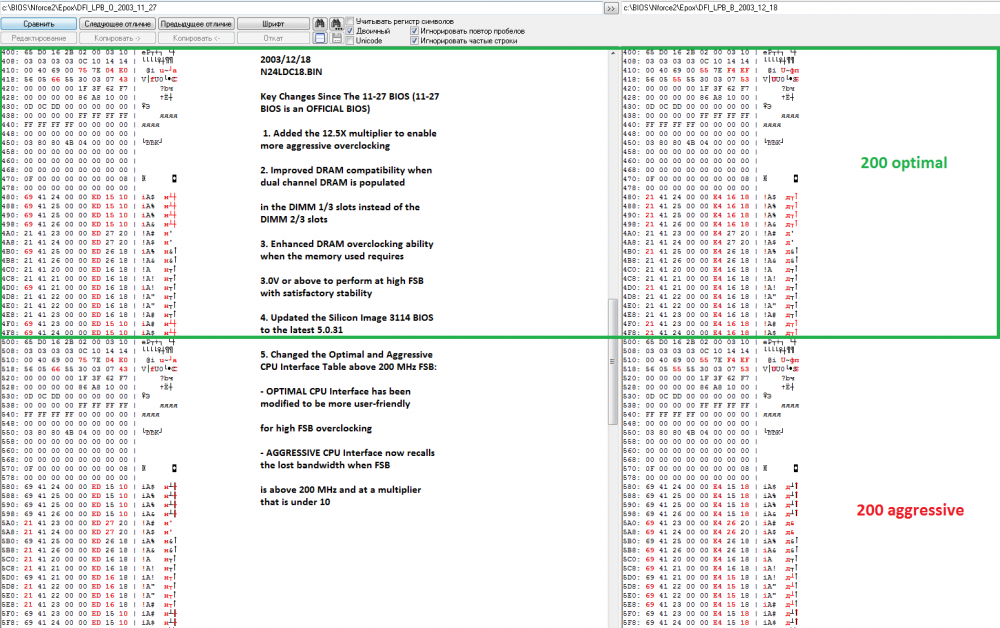

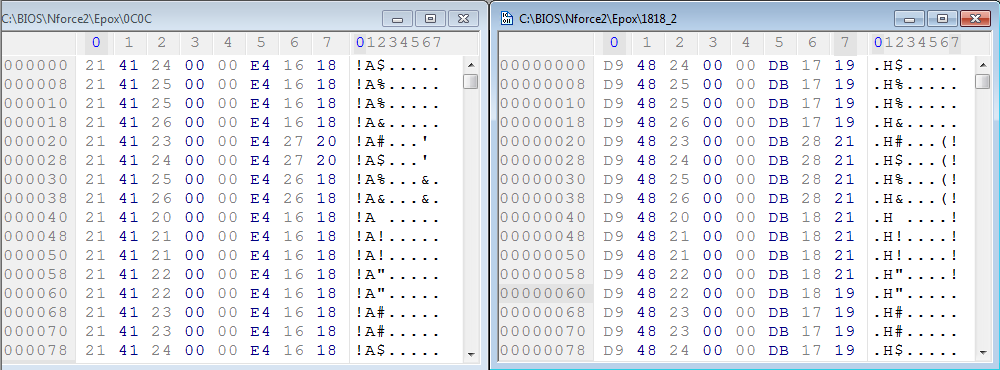

Another interesting attack vector is BIOS changelogs. Here is a compare between two DFI BIOSes and their changelog. Looks like the last line about bandwidth refers to changes in offset 5D0h - 1618 has been modified to 1518. Which according to previous data should be SYSDCIN delay (6 -> 5).

CPU optimal is said to be more FSB friendly.

We can see two things - zero byte (in CPU multi ROMSIP lines) is changed from 69 to 21, byte 5 is changed ED -> E4. Looks like 69 is more aggressive than 21. E4 and ED are known to be of same efficiency maybe it's fine tuning with minor changes.

Another interesting thing are changes in chipset part of ROMSIP. Some changes are mapped by @digitalbath :

Some are still to be figured out.DFI changelist might be handy: https://forums.overclockersclub.com/topic/115082-dfi-nf2-bioses/

-

3

3

-

3

3

-

-

2 hours ago, TASOS said:

submitted to wrong cpu category.

Well noted. Moved and checked them all.

-

Apollo 266 with SDRAM, interesting choice. Nice result.

-

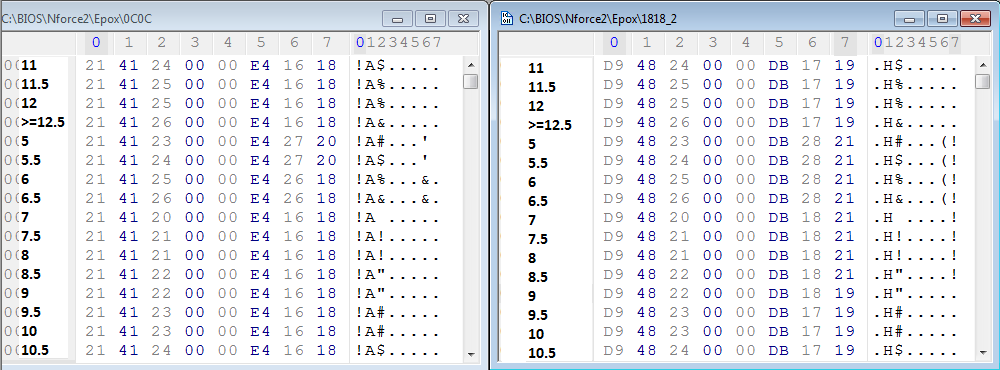

O.K. looks like I've found the byte 2. This table sure looks familiar if you compare with byte 2 table from above.

Still, a long read is ahead. I think I'll take a break.

P.S. found a nice list of AMD datasheets, gotta make a local copy of that: https://en.wikichip.org/wiki/amd/List_of_AMD_publications

-

3

3

-

-

13 minutes ago, digitalbath said:

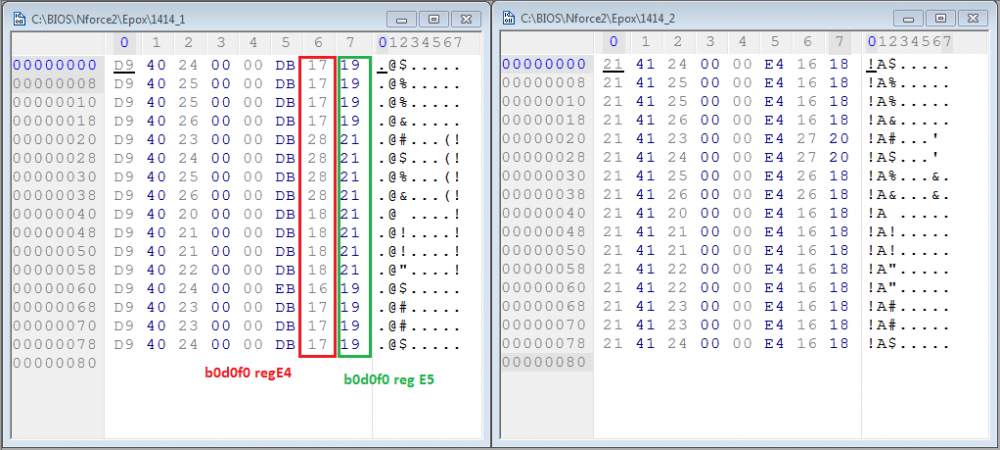

As far as I tested, faster sips E4, ED needs lower values like 1618 or 1518. Slower sips like DB needs higher numbers like 1719 or 1821. You can change the last number from 1518 to 1519 and it will work.

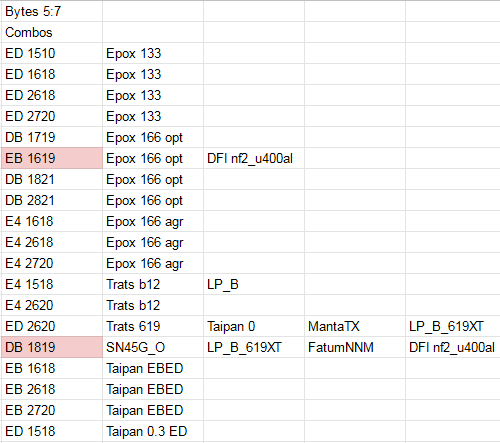

I've made a list from ROMSIPs you've sent - Trats, Shuttle, Taipan, Manta TX, LP_B_619, k12r4, DFI U400s-al, DFI_LP_B (all of them). Here are all the combos for last three bytes:

Reds are what I think as typos, anomalies. Though, might help in the research.

-

2

2

-

-

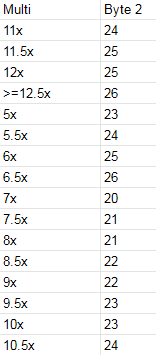

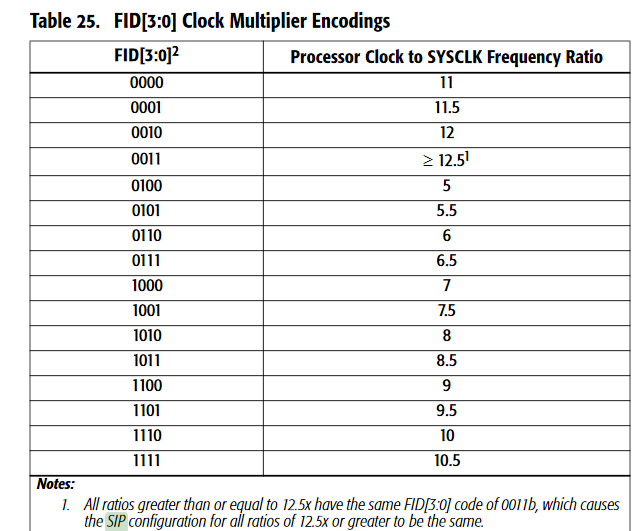

O.K. CPU multi part byte 2. Looks like byte 2 is always the same in ROMSIP and depends only on multi:

After that, bytes 3 and 4 are 00.

But there is one notable exception - DFI (and ECS) that use another writing, in fact, two of them.

First is a usual ROMSIP entry, second is an entry modified by DFI, let's call it 3A 02 (by bytes 3-4). The third is another DFI entry, I'll call it CA 02.

As you can see, in all cases byte 2 remains the same, only bit 7 is set to 1.

In 3A 02 byte 1 bit 5 is set to 1, bytes 3 and 4 are 3A 02.

In CA 02 byte 1 bits 5 and 3 are set to 1, bytes 3 and 4 are CA 02.

Do not, that only these bits in byte 1 are modified. Other bits depend on byte 0 that are use for optimal/aggressive settings.

Purpose of these bytes is unkown AFAIK but feel free to test DFIs modded settings.-

3

3

-

-

16 hours ago, TerraRaptor said:

I was expecting the last two registers (like 16 18 or 26 18) to be drive strengths for receiver/transmitter aka cpu side and NB side.

Were you able to set any combinations of values? Seems like they're tied together and you can't set random numbers. Maybe it's my setup.

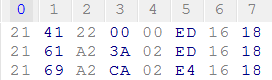

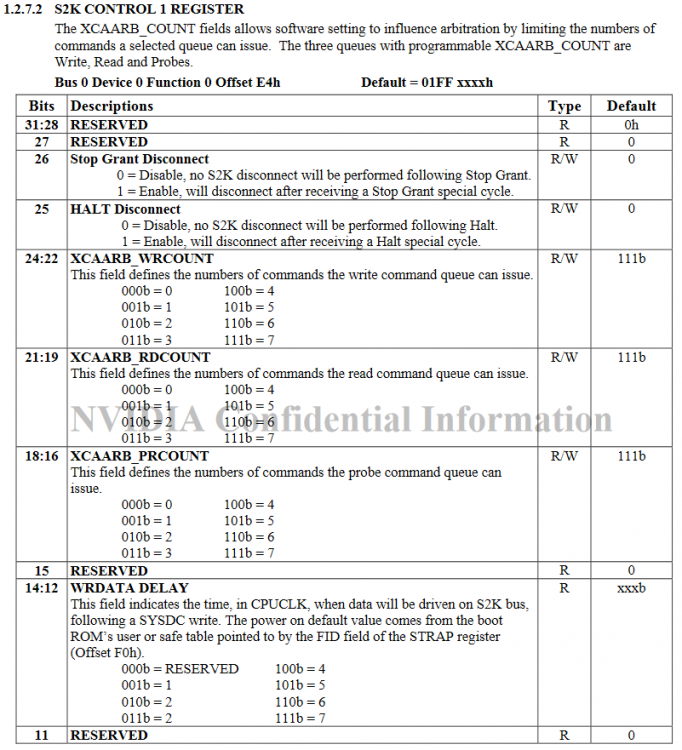

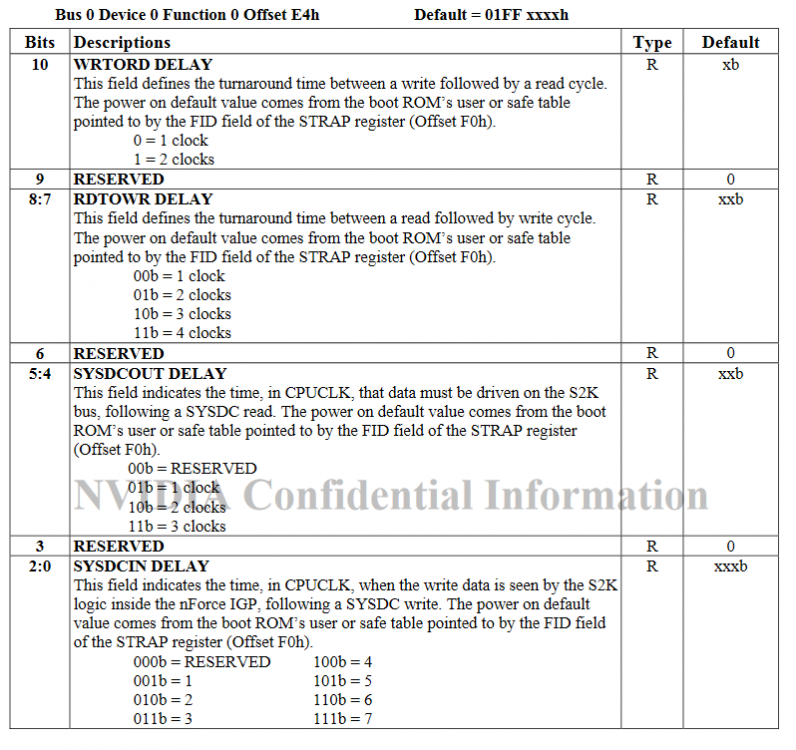

OK, the last three bytes of each multiplier in CPU part of ROMSIP are connected to b0d0f0 rE4-E7. Whice is S2K CONTROL 1 REGISTER. It configures timings of S2K (EV6) bus. But you can't change any bit in the ROMSIP, they are connected somehow. I've had a E4 1618 and tried a E4 1719 setting (1719 from optimal), it didn't POST. Then I changed it to BD 1719 (full three last bytes from optimal) and it worked.

Counting from zero, the 6th byte is reg E4 (except the 7th bit).

7th ROMSIP CPU multi byte is reg E5 (with a mask). byte 7 bit 0 is reg E4 bit 7 (RD2WR delay).

byte 7 bits 5:3 are reg E5 bits 6:4

Now I need to check ROMSIPs for valid byte combos.

So byte 6 controls SYSDCOUT delay and SYSDCIN delay.

Byte 7 controls W2R delay and WR data delay.

Some ROMSIP bits seem unused by the registers, maybe they control some other regs maybe combined with byte 5.

-

3

3

-

-

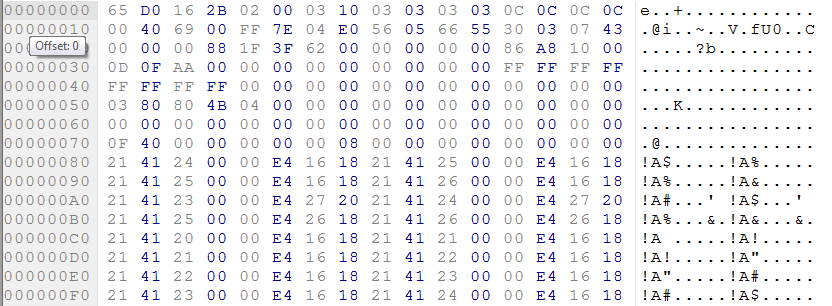

I'll start myself with the ROMsips.

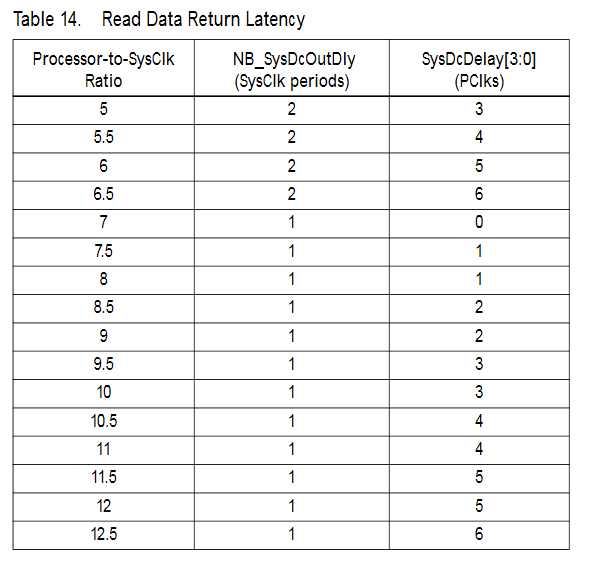

I believe that the table consists of two parts - the first part is chipset-related. The second part is CPU-related. The main problem was that I've been trying to match multipliers to CPU part of the table.

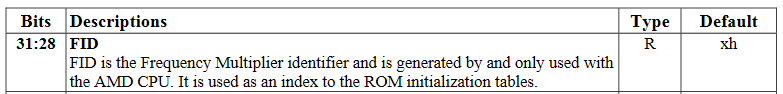

Then I've remembered this part. And I've understood that FID isn't endoded in ROMSIP. Instead, FID itself is a link to ROMSIP. Let's look at FID table:

So, all multipliers are represented by 16 values that are used by SIP (serial initialization protocol, which is quite advanced). And now take a look at the CPU part of ROMSIP:

Do you see this? Multis 11-12,5 (and all higher) have same last two bytes, then 5x and 5.5x are different. The first ROMSIP uses different settings for 6x, 6.5x but the second one has same settings as 5x, 5.5x.

So these do look like CPU settings. I believe some of them are delays that are programmed during SIP packet.

Might be lame, but I didn't see this info before.-

3

3

-

-

Hello, I'd like to separate some in-depth research considering sA that started in this thread: https://community.hwbot.org/topic/187148-a7n8x-e-deluxe-as-an-alternative-for-socket-462/

I'd like to discuss some sA and NF2 specific mods to:

- Make instructions for beginners

- Investigate other BIOS mods

- Make some progress if possible

I'd like to investigate the work done by gurus like Merlin, tictac and many others, take the best from them and maybe move ahead.

It would be very nice to get over 250FSB by tuning system registers and check how it's done.I'll start with some known mods and would like those familiar with ( @Mr.Scott ,@I.nfraR.ed, @digitalbath, @Tzk, @Strunkenbold, @TerraRaptor) to check in and correct if I'm wrong:

- BPL mod (also NVMM in later versions) - memory init routine from NV. Newer versions are better (up to 3.19?), latest are sometimes incompatible. CPC off (=CR 2T) seems to be modded in BPL.

- ROMSIP - a set of tables (CPU interface on/off, and for 100/133/166/200 FSB) with CPU and chipset related settings. Influence stability, overclocking, performance.

- soft-L12 - a mod that acts as BSEL, forcing BIOS to implement FSB200 settings even on FSB133 CPUs. Most mod BIOSes have it, add stability on high bus speeds.

- modified alpha-timings (can be set using the new NF2 tweaker from Infrared)

- options ROMs with performance tweaks (3D-fire for example - modified chipset registers?)

- changed some northbridge registers (S2K control probe limit, XCAARB_RD/WRCOUNT, DQSEN_PULL_B, Auto Refresh Cycle Time, Read-to-Read Command Latency, Pre-charge All Command ) (seen on Asus A7N8X dlx mod BIOS)

Please, stay to the topic, don't discuss CPU binning, memory, voltmods and other things. BIOS mods and how they affect the system is the primary goal. Do not discuss cosmetics and general BIOS techniques like opROM update, unlocking menus and so on. I believe we all know how this is done (or it can be discussed in a different topic) so we can focus on advanced stuff.

Infrared's Discord channel about Socket A: https://discord.gg/YKHvEt6xctSummary of nf2 registers: https://docs.google.com/spreadsheets/d/1ZDST3XGq0oE7YtQxAME29RtopA8QcePCaHa2NBRHaB8/edit#gid=0

-

6

6

-

3

3

Official HWBOT Team CUP 2021 thread:

in HWBOT Competitions

Posted

Well, FB-DIMM use DDR2 technology, it's just a specific branch yet still DDR2 that's why I asked to confirm. Thank you.