TerraRaptor

Members-

Posts

1994 -

Joined

-

Last visited

-

Days Won

51

Content Type

Profiles

Forums

Events

Blogs

Everything posted by TerraRaptor

-

The official HWBot Team Cup 2020 Memfreq thread.

TerraRaptor replied to ksateaaa23's topic in HWBOT Competitions

Правильно указать объем надо - 16348, а не 16384. -

keeph8n - Core i9 10900K @ 7347MHz - 4min 5sec 516ms SuperPi - 32M

TerraRaptor replied to AKM's topic in Result Discussions

Woot! -

Is this degradation? PSC/haswell/air

TerraRaptor replied to nnimrod's topic in Memory Heaven (air/extreme)

32m alone is not really telling on stability. The tighter you go, more surprises you get - and sometimes you need to go back and revalidate stability of previously adjusted timing you thought is stable as the timing you are adjusting now is affecting in as co-dependence. I was using multithreaded tests (hyperpi, hci memtest) as it gives better idea of stability. -

Nik - Core i7 8086K @ 7200MHz - 4min 13sec 922ms SuperPi - 32M

TerraRaptor replied to Brutek's topic in Result Discussions

Well done Nik! -

Memory benchmarks by IC?

TerraRaptor replied to nnimrod's topic in HWBOT Development: bugs, features and suggestions

Not always that, sad but true. -

A7N8X-E Deluxe as an alternative for socket 462

TerraRaptor replied to TerraRaptor's topic in Mainboards

Make it validate 300mhz it it will go quickly:) -

TerraRaptor - Celeron 420 @ 4000MHz - 14sec 985ms SuperPi - 1M

TerraRaptor replied to 12's topic in Result Discussions

Removed them to help insulation and check how it affects OC. Result is it helps insulation and no effect on OC. Slots 1+3 are way worse with this sample, also very big drop in stability if all 4 slots were occupied - so no sense to have it anyway. -

It was pretty strong kit (2666c8 tight air, 2850c6 tight LN2) so I agree it should be temperature limited even with SS. In the end, even below average kit of hypers is better than LN2 psc in x48 imho.

-

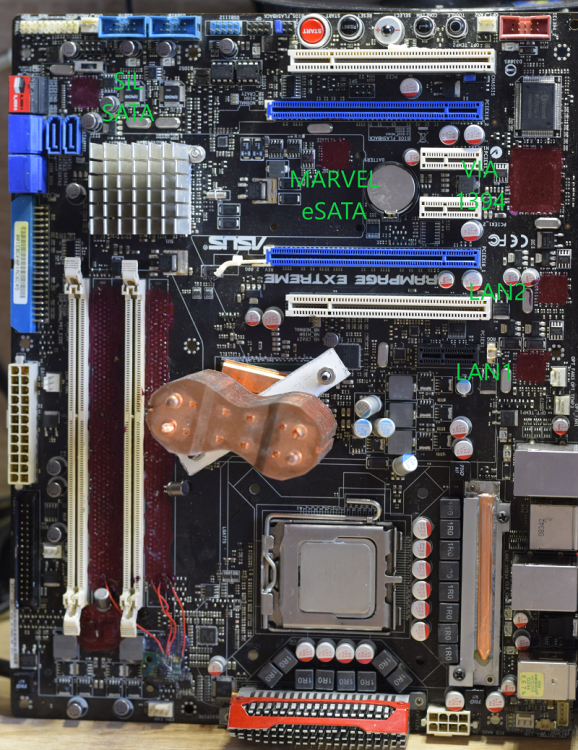

Disclaimer: all information here is my experience, I will be not responsible for any damage that may be there if you follow any instructions here. Environment and general settings · Replace stock/old TIM on NB – many OCers report that replacing stock TIM on NB helped them a lot. I would aim for <50C NB temperature in BIOS for any settings. Some stock coolers may have issues and may require dremel works to get good contact between NB IHS and cooler. Try software named MCHTemp to control overheating of NB – if too hot, NB may throttle and/or have limited FSB overclocks. Another point to consider – when measuring dc resistance, NB is 8Ohm @30C and 4Ohm @50C – so thermals should rise dramatically the hotter NB is. · Disable most CPU features (EIST, TM2, etc), disable jMicron etc. To enhance boot time, you can disable unused sata ports etc. To get very slight performance boost in SuperPi 1M, use modded bios with 45nm microcodes removed (it cuts 0.200-0.250 seconds off bios with ucodes included with E8xxx @4GHz). · Pay attention to capacitors. REX is known to have issues with aged Fujitsu caps – there are 3 pcs (one each for CPU, DRAM, NB). Seems like the higher voltage is, the faster these fujitsu caps die – so most affected cap is DRAM cap, if you go hard with LN2 then CPU cap is next candidate to die (I had one blown during LN2 session when I pushed 1.95v into cpu). I had no issues with NB caps yet but saw other people having troubles with it. I suggest that DRAM cap should be preventatively replaced with 2*470uF tantalum caps – do not use long wires to connect classic type capacitors. Not sure about the other two should be replaced before they fail – though cap running into short circuit may lead to VRM misbehavior that will kill the chip. I had also issue with 16V caps near USB headers – these were getting really hot. So you should probably check temperature of all solid caps with finger while running the board at stock settings for 5-10 minutes (note – not a single capacitor should be hot). Here is a photo of all the secondary controllers that are connected to ICH9R and may be removed to minimize chances that one day it would damage SB. Getting higher FSB If you want really high FSB, make sure you pump enough Vcore. It means that if your cpu needs 1.25v for 500x8, you will probably need same 1.25v for 533x7.5 but closer you get to and beyond 600Mhz the higher Vcore is needed –I used 1.700-1.725v during my attempts to break 700MHz FSB (it was balance of temperature and voltage). Again, cpu voltage is necessary for FSB so if your CPU needs 1.25v for 500x9, it will likely need 1.5v for 625x6 (although core is 750MHz lower). Another important thing to consider are CPU and NB skews. It is core dependant, yet here is some empiric data I have with my CPUs (it varies a bit but still may give you an idea): · Core 2 Quad Q8xxx/Q9xxx needs these to be manually adjusted to 200/0 or 200/100 at 500Mhz and probably further adjustment the higher you go. · Core 2 Duo e8xxx seems to need adjustments after 600Mhz. 600MHz is 200/0, 625 is 300/0, 643 is 400/100 etc. Also, a thing that may help you to run tests higher are GTLREF settings. REX has 4 lanes for CPU, gtlref is derived as a factor of VTT. It is important to note the following coefficients are used when these are “auto” in bios: CPU GTLREF 0 – 0.65xxx of VTT CPU GTLREF 1 – 0.67xxx of VTT CPU GTLREF 2 – 0.65xxx of VTT CPU GTLREF 3 – 0.67xxx of VTT You can get a more precise value of these numbers by measurements. All you need is to start the board after CMOS reset, enter bios and run measurements one after another – Vtt and GTL lanes. Now divide measured GTL by VTT and you will get the precise value your board has by default. During OC, the task is to keep a pair of GTL0>L1 (cores 0+1) and a pair of GTL2>L3 (cores 2+3) as close as possible within a given pair. The easiest way to estimate what difference should you set in bios is the following equation: (0.67xxx-0.65xxx)xVTT – that is why measurement of your board sample may be helpful. I have 0.003v deviation between GTL1 & GTL3 for example @1.1v VTT. Roughly, it makes the difference of as 0.02xVTT. So if you run 1.55v VTT, you are recommended to make you GTL0 1.55*0.02=0.031V higher to match GTL1. It translates into closest BIOS value +30/auto setting if you aim x0.67 GTL, +80/+50 will translate into x0.70GTL etc. As a side note, P45 boards seem to benefit from x0.61-0.63 CPUGTL but it still requires tests with x48 (though I was pretty good with -10/-40 when pushing E8200 - translating into x0.65 multi). Things that still need to be discovered voltage-wise are NBGTL (should affect FSB), dram reference voltages, NBDDRref (should affect dram oc). No serious tests from me, usually trials&errors only. Tricks that may be of help sometimes The trick that gave me the last 2MHz over 700MHz valid – setting clock overcharge voltage (in terms of asus p45) higher. This setting is a function of clock generator and defines an amplitude of clock that is being fed into CPU. As this setting is missing in bios of REX, you can change it in windows with SETFSB. Go to diagnose tab, read clocks and then select byte 01. The last (see image for reference) 2 bits seem to be responsible for cpu clock amplitude setting: 00 – 600mV 01 – 700 mV 10 – 800mV 11 – 900/1000 mV Set 2 bits, click update, click apply. This is nothing critical, but if you check DFI P45 threads you will see some people have gains with it (setting is available for DFI by default). vPLL mod – described DRAM skews – these will affect stability closer and over to 2000MHz. Some information will follow in next chapter. My experience with different DRAM IC for 4GHz low clock challenge Well, most REX boards should be able to overclock 2x2GB dual-sided RAM to 2000MHz – the only difference between boards is how tight it can go with a given set of RAM (if RAM is not limiting factor). Key factor is a so called performance level (which is strap/fsb/CL dependant – so if you change one, PL should be adjusted accordingly). Please note that you should use white slots to get best OC results in most cases. Here are my tests with different DRAM ICs that were done within the limits of 4GHz low clock challenge (so the choice of settings for FSB were 500x8, 533x7.5, 572x7). I was aiming for the highest possible dram frequency for each IC type. Elpida BBSE, SS-cooling: https://hwbot.org/submission/4489967_terraraptor_superpi___32m_core_2_duo_e8200_10min_50sec_688ms These are pretty good performers although will have limited voltage tolerance. I have tested 12 different sticks, most won’t post if dram voltage is over 1.75-1.775v. It was important to adjust dram skew latencies to make it work with that high frequency – the difference was 25ps B2 delay was allowing me to pass 32M without errors multiple times after boot while 0ps/75ps B2 delay wasn’t able to just boot into WinXP. NBDDRref of -10mV also helped a bit. Note: BBSE used is pretty strong, one of the highest bins from G.Skill. Micron D9GTS, ss-cooling: hwbot.org/submission/4489977_terraraptor_superpi___32m_core_2_duo_e8200_10min_52sec_188ms These won’t go even 1000MHz being dual-ranked microns. Still performance is acceptable. As the frequency is low, no special adjustments necessary to skews or secondary voltages – pretty easy in use. Samsung G-die, air-cooling (seems have poor temperature scaling anyway): hwbot.org/submission/4489990_terraraptor_superpi___32m_core_2_duo_e8200_11min_3sec_937ms These are pretty easy too, although performance is not stellar. Scale from voltage, not hot even with 2.3V. I would recommend these for debugging purposes but performance-wise these are much weaker than hypers/bbse/micron. Elpida Hyper, ss-cooling: https://hwbot.org/submission/4490001_terraraptor_superpi___32m_core_2_duo_e8200_10min_47sec_546ms Wasn’t able to make it stable over 1000MHz, although it posts 1066/1144 and I was able to run pifast @1144 before. The best choice for X48 anyway. Allows low tRCD, tRFC, PL. Scales with volts. PSC X-sreies, ss-cooling: https://hwbot.org/submission/4490004_terraraptor_superpi___32m_core_2_duo_e8200_10min_53sec_187ms Absolute nightmare in my tests. Voltage intolerant, won’t accept anything over 1.65v (confirmed by Mythical Tech although he was happy with cold PSC in REX). Too difficult to manage these work properly, I would go with bbse/micron instead.

- 16 replies

-

- 28

-

-