-

Posts

2473 -

Joined

-

Last visited

-

Days Won

36

Content Type

Profiles

Forums

Events

Blogs

Everything posted by I.nfraR.ed

-

A7N8X-E Deluxe as an alternative for socket 462

I.nfraR.ed replied to TerraRaptor's topic in Mainboards

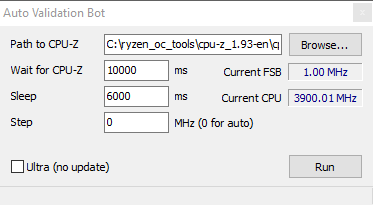

Who's up to some auto overclocking and validating https://github.com/irusanov/nForce2-xtreme-tweaker-vcl/releases/tag/beta-12 This includes Auto Validation Bot and some initial code for configurable INI files. settings.ini is included in the archive, but you can only control "minimizeToTray" - 0 means false, 1 is true. There's no GUI for settings yet and nothing is implemented regarding profiles, but getting there. None of the settings of the Auto Validation are saved, you have to configure them on each launch of the tweaker. For now, there are some limitations I haven't been able to fix regarding of the detection whether cpuz has fully loaded. So, in order to try the "bot", you need to first configure settings: Path to CPU-Z -> select path to cpuz executable Wait for CPU-Z -> time in milliseconds to wait for cpu-z launch 1s = 1000ms Sleep -> time to sleep between validations. It is needed, so we give time for cpuz to save the file, recent versions are very slow in this regard, so you might need to even increase this value Step -> tweaker will try to find the next FSB which is currentFSB + step. 0 is for auto and will take longest time. Ultra -> this won't update CPU frequency and FSB in the tweaker, should be lightest mode When configured, click "Run" and don't touch anything anymore. CPU-Z window needs to have the focus, so the validation works. You can manually switch to another CPU-Z tab and validation should still work. Not sure if that would reduce the load though. To stop it, click on "Stop" and close CPU-Z window manually. PS: I think it is obvious that this feature would lead to a BSOD at some point when the limit of some component is reached - whether it is CPU, RAM or FSB. It goes until crash/BSOD or manual stop. Also not sure if that would allow a higher validation compared to doing it manually, but I think it should, since it eliminates clicking on buttons and switching between windows. Either way, it's a fun experiment . -

A new way to address CPUs (Cores/Threads) on HWBot

I.nfraR.ed replied to der8auer's topic in HWBOT 2021 Edition

Let me stir it a bit more. Big.LITTLE doesn't mean just two complexes of equal cores anymore. Just one example (yes, first 4 cores are still A78, but one is clocked higher and has twice the L2 cache). They probably can't be overclocked by the user. Would a similar desktop CPU able to compete in the single-core global category if it is possible to disable the rest of the cores? MediaTek MT6893 Dimensity 1200 5G (6 nm) 1X Ultra Core: Arm Cortex-A78 up to 3GHz with 2X L2 cache 3X Super Cores: Arm Cortex-A78 up to 2.6GHz 4X Efficiency Cores: Arm Cortex-A55 up to 2GHz Mediatek calls it 8-core. There are also other models with 2 high performance cores + 6 efficient cores = still a octa-core CPU. -

A7N8X-E Deluxe as an alternative for socket 462

I.nfraR.ed replied to TerraRaptor's topic in Mainboards

It's me again, beta 11 adds ability to set AGP/PCI frequency as well. It has most of the functionality I want. It even has a better granularity for the FSB frequency than clockgen. What's left is to add ability to save and load OC profiles, complete the CPU detection/info and add some options like "minimize to tray". NForce2Xtreme-v1.1-beta11.zip- 533 replies

-

- 11

-

-

-

Windows XP on Ryzen 5800X / B550 board

I.nfraR.ed replied to Masterchief79's topic in Ryzen | Bristol Ridge AM4

Pi 32M is slow, could not get wazza working. Other than that, haven't tried legacy 3D, but it might be useful for cards where XP drivers are better. It looks you're running in "Standard PC" mode though. PS: It seems cpuz is wrong with the threads? -

A7N8X-E Deluxe as an alternative for socket 462

I.nfraR.ed replied to TerraRaptor's topic in Mainboards

New version of the tweaker. FSB should now work. beta9 corrects some timings not set correctly, sorry for the inconvenience. Also found how to control AGP/PCI frequency and will probably implement it next. NForce2Xtreme-v1.1-beta8.zip NForce2Xtreme-v1.1-beta9.zip -

I'm not sure if it is still the case, but removememory command has another advantage over maxmem from msconfig. If you set a maxmem value and want to increase it, then you need to delete the old value first, then reboot, set the larger value and reboot again. However, if you have clocked your B-Die with high voltage it would BSOD after first reboot (full memory capacity) and you have to reduce the clock/voltage. With removememory you can simply set a new value and reboot.

-

B550 Unify-X Bios and Tools

I.nfraR.ed replied to SparkysAdventure's topic in Ryzen | Bristol Ridge AM4

The bad thing about this tools is that it's x64 only. The only app that works on 32bit Windows I know of is ZenStates, but it has limited functionality and requires vcore in "AMD Overclocking" mode, not fixed. That's if you want to change VID. You can always set frequency. -

A7N8X-E Deluxe as an alternative for socket 462

I.nfraR.ed replied to TerraRaptor's topic in Mainboards

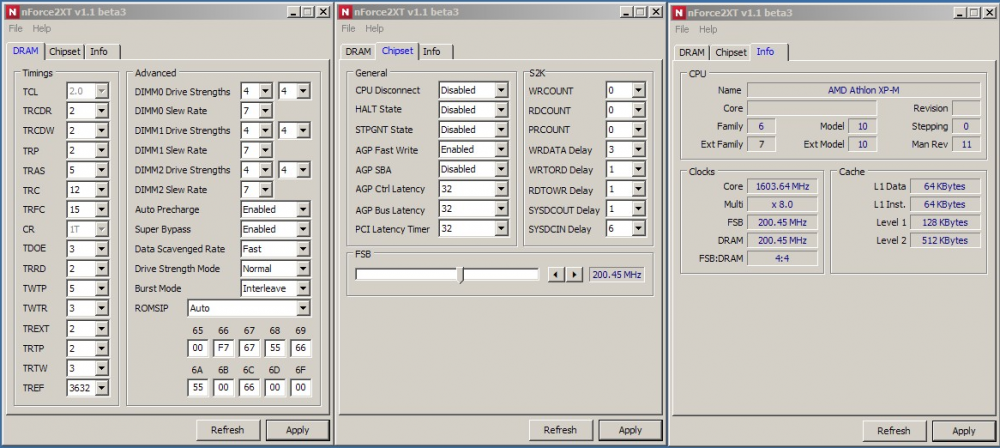

New version of the tweaker. Started from scratch and ported all the functionality from the previous app. This is a native one and doesn't need .NET framework, which results in much faster start up. There are several improvements and new settings, FSB slider doesn't do anything yet. Source: https://github.com/irusanov/nForce2-xtreme-tweaker-vcl NForce2Xtreme-v1.1-beta3.zip -

I have encountered the same thing while developing the nf2 tweaker. When booted with 1:1 you can then "set" any FSB:DRAM ratio and cpuz is easily fooled, because it seems to read that register. https://valid.x86.fr/zukryk I've obviously exaggerated "a bit" with the 3508MHz (DDR-7016). 1:15 is the highest possible. CBID tool is reading DRAM frequency correctly, so I'm trying to find how to reproduce it and report to Franck. Makes me question the validity of the current top-1 valid for socket A (except that one of from @digitalbath). Not calling anyone cheater, but it might be another honest mistake. The thing is we were all stuck at 300.7 max, while the Greeks managed higher. Not saying it's impossible though.

-

Is that supposed to be a hidden thread? I don't see the competition listed yet and it seems some people see the stage limitations...

-

True. I was expecting minor revision to be higher for newer CPUs, but it seems there's no such correlation. There's also no correlation between the minor revision, the PCB revision and the gold letter in the corner. Common versions for Barton are 2, 11, 12, 15 and as @Tzkpreviously wrote, 12 and 15 are reported as unlocked, while 2 and 11 are reported as locked. This doesn't 100% correspond to reality, since it depends on the production week, too. One of my 2s are unlocked and one 12 is locked. Overall the detection success rate seems to be high. I will re-check those 2 CPUs to make sure it's not an error on my side. Thoroughbred B has revisions 2, 6, 13, 14. 2 and 6 are reported as "Unknown", 13 is reported as "Undetermined" and 14 as "Unlocked". In reality, 13 seems to be the only one that is locked. 2 and 6 seem to be from 2002, others are 2003 and 2004. There's one 14 from 2002. I have one Applebred B0 (Thoroughbred-B) which is 14 and is locked, produced in week 0347. All Thoroughbred-B Semprons I have are 13 and are locked. Also later production weeks, which "guarantees" a super locked CPU. 11 is B in HEX, 12 is C, 13 is D, 14 is E, 15 is F. I guess the highest possible is 15 (F). According to the documentation, it's bits 3-0 (4 bits), so 1111 = F is the highest. Edit: For Applebred/Thoroughbred the following seems to be valid (with one exception again, which I have to recheck) xxxHB (e.g. JIUHB) is 14 xxxCB (e.g. JIUCB) is 6 xxxJB (e.g. KIXJB) is 13 xxxXB (e.g. MCXB) is 13 xxxGB (e.g. AIUGB) is 2 I'm sure BCRC is guessing the "Crystal Marker" based on the minor revision and codename. The theory is that this minor revision is something like a range of letters. Same applies to the major revision, which is indicated from the last letter, e.g. JIUHB, where B = 1 for "Thoroughbred-B". In case of a Barton, we have A = 0 there, e.g. IQYHA. I'm kind of sure about last letter now. The minor revision is probably "encoding" for more than one letter. This timeline with steppings might help us reconstruct the lookup table: https://www.cpu-world.com/info/AMD/amd_stepping_K7.html https://www.cpu-world.com/info/AMD/K7_stepping_codes.html

-

I bought it mostly for the board, the CPUs are not interesting. The board capabilities are unknown until properly tested. Free up

-

I've been going through some of my CPUs. I forgot to note the reported core by BCRC for some of the first entries in the table, so take them with a grain of salt. The lookup table for those cores is not 100% correct anyway. Some of my Thoroughbreds are missing, hopefully I will find where they are Model OPN Batch Core CPUID Rev Unlocked Code Name Site.Major.Minor Multiplier type Possible Marker Athlon XP 1700+ AXDA1700DLT3C AIUGA 0245SPIW Thoroughbred-A 0680 A0 yes 2308 Thoroughbred 1.0.4 Unknown Unknown Athlon XP 1700+ AXDA1700DLT3C AIRGA 0319WPMW Thoroughbred-A 0680 A0 yes 2318 Thoroughbred 1.0.14 Locked MIAGA Athlon XP 1700+ AXDA1700DLT3C RIRGA 0233VPMW Thoroughbred-A 0680 A0 yes 2318 Thoroughbred 1.0.14 Locked MIAGA Athlon XP 1700+ AXDA1700DLT3C JIUHB 0320MPMW Thoroughbred-B 0681 B0 yes 2334 Thoroughbred 1.1.14 Unlocked AIUHB/JIUHB Athlon XP 1700+ AXDA1700DLT3C JIUHB 0323RPMW Thoroughbred-B 0681 B0 yes 2334 Thoroughbred 1.1.14 Unlocked AIUHB/JIUHB Athlon XP 1700+ AXDA1700DUT3C JIUHB 0312XPFW Thoroughbred-B 0681 B0 yes 2334 Thoroughbred 1.1.14 Unlocked AIUHB/JIUHB Athlon XP 1700+ AXDA1700DUT3C JIUCB 0251TPXW Thoroughbred-B 0681 B0 yes 2326 Thoroughbred 1.1.6 Unknown Unknown Athlon XP 1800+ AXDA1800DLT3C JIUHB 0310MPMW Thoroughbred-B 0681 B0 yes 2334 Thoroughbred 1.1.14 Unlocked AIUHB/JIUHB Athlon XP 1800+ AXDA1800DLT3C JIUHB 0333VPMW Thoroughbred-B 0681 B0 yes 2334 Thoroughbred 1.1.14 Unlocked AIUHB/JIUHB Athlon XP 2000+ AXDC2000DUT3C AQZFA 0343UPMW Thorton 06A0 A2 no 2306 {empty} 1.0.2 Locked AQYFA Athlon XP 2000+ AXDC2000DUT3C AQXEA 0324UPMW Thorton 06A0 A2 yes 2316 Thorton 1.0.12 Unlocked Unknown Athlon XP 2000+ AXDA2000DUT3C KIXJB 0415EPMW Thoroughbred-B 0681 B0 no 2333 Thoroughbred 1.1.13 Undetermined JIXIB/AIXJB Athlon XP 2000+ AXDA2000DKV3C JIUHB 0338MPM Thoroughbred-A 0680 A0 yes 2308 Thoroughbred 1.0.4 Unknown Unknown Athlon XP 2100+ AXDA2100DUT3C AIUHB 0302WPDW Thoroughbred-B 0681 B0 yes 2334 Thoroughbred 1.1.14 Unlocked AIUHB/JIUHB Athlon XP 2100+ AXDA2100DUT3C JIUHB 0308VPMW Thoroughbred-B 0681 B0 yes 2334 Thoroughbred 1.1.14 Unlocked AIUHB/JIUHB Athlon XP 2200+ AXDA2200DUV3C AIUCB 0240RPFW Thoroughbred-B 0681 B0 yes 2326 Thoroughbred 1.1.6 Unknown Unknown Athlon XP 2400+ AXDC2400DKV3C AQXFA 0348MPMW Thorton 06A0 A2 no 2306 {empty} 1.0.2 Locked AQYFA Athlon XP 2400+ AXDA2400DKV3C AIXHB 0328SPGW Thoroughbred-B 0681 B0 yes 2334 Thoroughbred 1.1.14 Unlocked AIUHB/JIUHB Athlon XP 2400+ AXDA2400DKV3C AIUGB 0244MPM Thoroughbred-B 0681 B0 yes 2322 1.1.2 Unknown Unknown Athlon XP 2500+ AXDA2500DKV4D AQYFA 0350SPGW Barton 06A0 A2 no 2315 Thorton w/512K 1.0.11 Locked AQYFA What I've seen so far: Reticle site is always 1 - it's either a mistake in the tweaker or these bits started to be meaningful from K8 and up Major mask revision is always the same as the stepping (read from CPUID) and the only core that has 1 instead of 0 is Thoroughbred B (as in "the 2nd revision of T-Bred core") Minor revision is the interesting one BCRC displays Barton if minor revision is 12 and Thorton w/512K when it is 11. Note that the CPU in red is FAKE Thoroughbred-B, in reality it's T-Bred A instead with L3, L5 and L12 bridges manipulated and has fake markings. Up to the "Unlocked" column are values either written on the cpu or detected from other tools. Unlocked column is based on testing. Rest of the columns are from BCRC and the tweaker. I will also check what Palomino reports, but that MSR is invalid on Thunderbird core, so maybe it's the same on Palominos. PS: Maybe we should use some shared google sheet, since you can't really format the tables here.

-

My boards are going down one by one without doing anything special, so I had to take the chance.

-

These "possible crystal marker" and "possible parent crystal" are just educated guesses based on other parameters. The multiplier type is also probably guessed based on some parameters (major.minor rev, but maybe something else too). That minor revision is kind of strange, I would have guessed higher minor revision would mean a newer cpu, but based on your table - that is not the case. I've added a message box to the tweaker on app open that displays the info I currently have implemented. There's not much info about the topic, but K8 KBDG (BIOS and Kernel Developer's Guide for AMD AthlonTM 64 and AMD OpteronTM Processors) has the MSR register in question documented There's one more value, which is "Reticle Site" and I've included it in the info. Curious to see what different cpus show. Btw, reading and writing MSRs is quite easy. You can use the MSR Editor and MSR Walker in CrystalCPUID tool. PS: I'm thinking of writing a small tool that automatically dumps CPUID registers, MSRs and all the info like cpuid, name, family, model, revision, etc. This way, the comparisons would be easier and faster. Edit: Replaced the app with new build. I was reading wrong part of the register, but it should be ok now. nForce2XT_Debug_20210703.zip

-

Yes, I've seen the same, but better structured changelogs, here: https://www.lejabeach.com/DFI/BIOS/dfiultrabbios.html I've compared them in the past, but not so extensively. There's a mention about "improved" 3D Mark 2001SE performance, but I don't know if the changes are in the romsip tables or somewhere else. Maybe it's worth checking performance of the bioses "as-is" on a real Ultra B first, with same manual settings on diffrerent benchmarks, but that's a lot of work. 2004/01/31 2. Increase 3DMark2001 SE performance (compare to 12/31) AFAIK that 15 10 doesn't work and it had been changed in most (all?) modbioses. Apparently Oskar Wu changed it too. I believe what you've shown on the right side should be close to optimal for all boards with all multipliers (the multiplier tables part). NF3 and NF4 bioses also use "E4", although I don't know how relevant it is.

-

Yes, tried different bioses and different values in the tweaker. I may install your modbios with the predefined romsip tables to check, but so far nothing helps.I can boot 260, but no stability, 255 is on the edge and usually experience a sudden force close while running a test (mostly on the "high" ones). 253 was ok. AGP bus up to 105MHz and voltage up to 1.8V didn't make a difference. Kind of want to try a KT880 board to see if it will be the same. I have a Delta-FSR somewhere in the closet.

-

Thanks. It seems HD3850 isn't very suitable for socket A. It's either a driver issue or it's a severe bottleneck by the platform. VGA overclock doesn't do much, mostly noticeable in Nature and that's what saves the day compared to e.g. a lower-tier nvidia card. CPU overclock doesn't help much either, I have similar scores on air-cooled CPU. I don't know why the "low" tests are so bad, especially car. FSB clock is the way to go and although this board can run 1M at close to 270MHz, it's really unstable above 250MHz with 3850. I also had to use the integrated SATA, since the VGA blocks both IDE ports and can't install the IDE-SATA adaptor. I guess one of my issues might be the modern PSU I'm using, had huge issues with CPU overclock. It is tested for 2.9 on ambient (3050 1M on chiller), but I couldn't even POST at 2.9. Had to clock it in windows. Also higher voltage was making it worse. I may try with 7800GS+, it will probably do better in other tests, not sure how it would compete in Nature. Ah, one more note - latest gpuz from the official site BSODs with gpuz-v2.sys or something like that.